TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-206

sc = (D[a][31:16] == 8000

H

) AND (D[b][31:16] == 8000

H

) AND (n == 1);

mul_res = sc ? 7FFFFFFF

H

: ((D[a][31:16] * D[b][31:16]) << n);

result = D[d] + mul_res + 8000

H

;

D[c] = {ssov(result,32)[31:16]), 16’b0}; // Short fraction

Status Flags

Examples

-

See Also

-

C Not set by these instructions.

V overflow = (result > 7FFFFFFF

H

) OR (result < -80000000

H

);

if (overflow) then PSW.V = 1 else PSW.V = 0;

SV if (overflow) then PSW.SV = 1 else PSW.SV = PSW.SV;

AV advanced_overflow = result[31] ^ result[30];

if (advanced_overflow) then PSW.AV = 1 else PSW.AV = 0;

SAV if (advanced_overflow) then PSW.SAV = 1 else PSW.SAV = PSW.SAV;

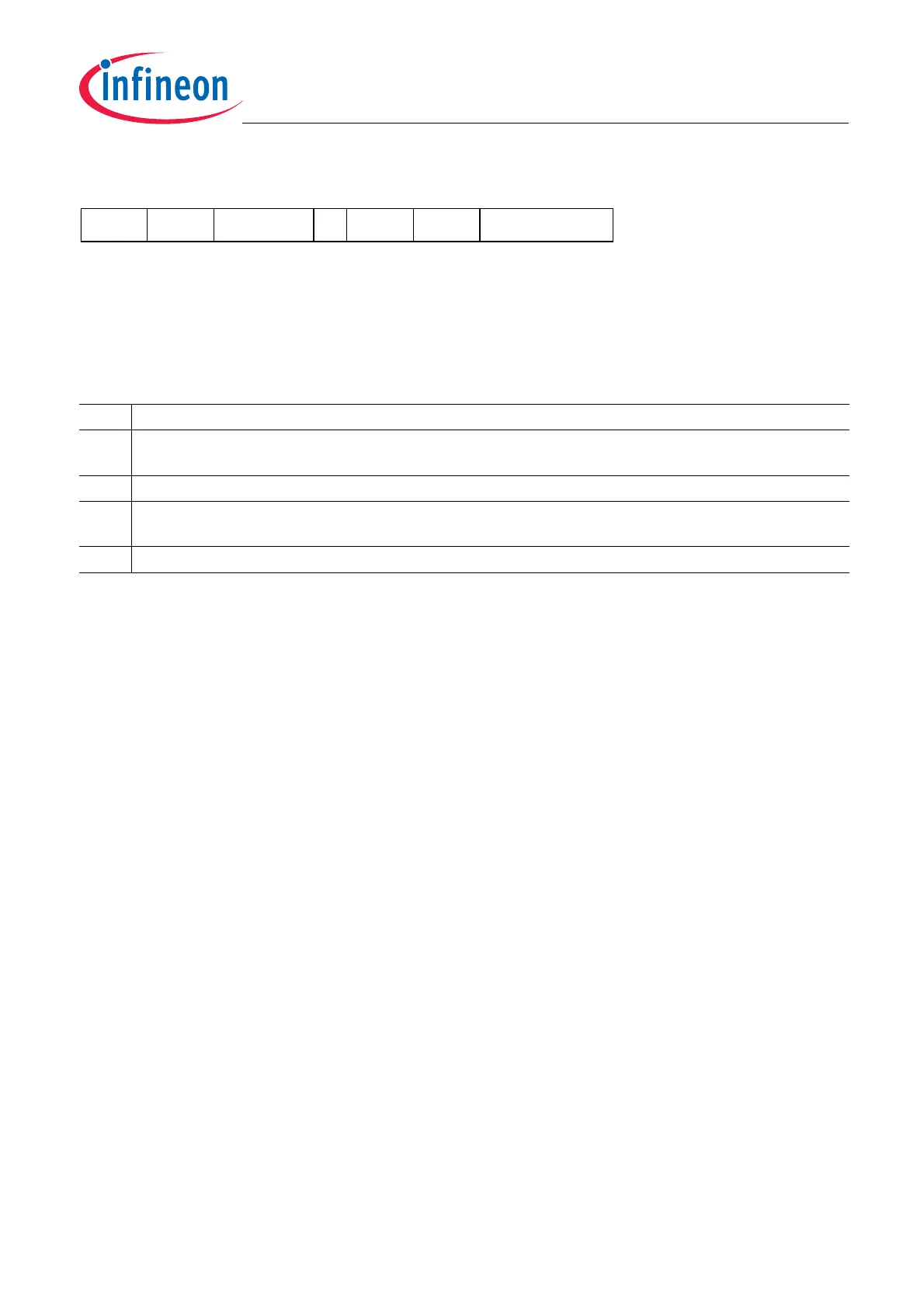

31

c

28 27

d

24 23

26

H

18 17

n

16 15

b

12 11

a

8 7

43

H

0

Loading...

Loading...