TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set Overview

V1.0 2013-07

User Manual (Volume 2) 2-19

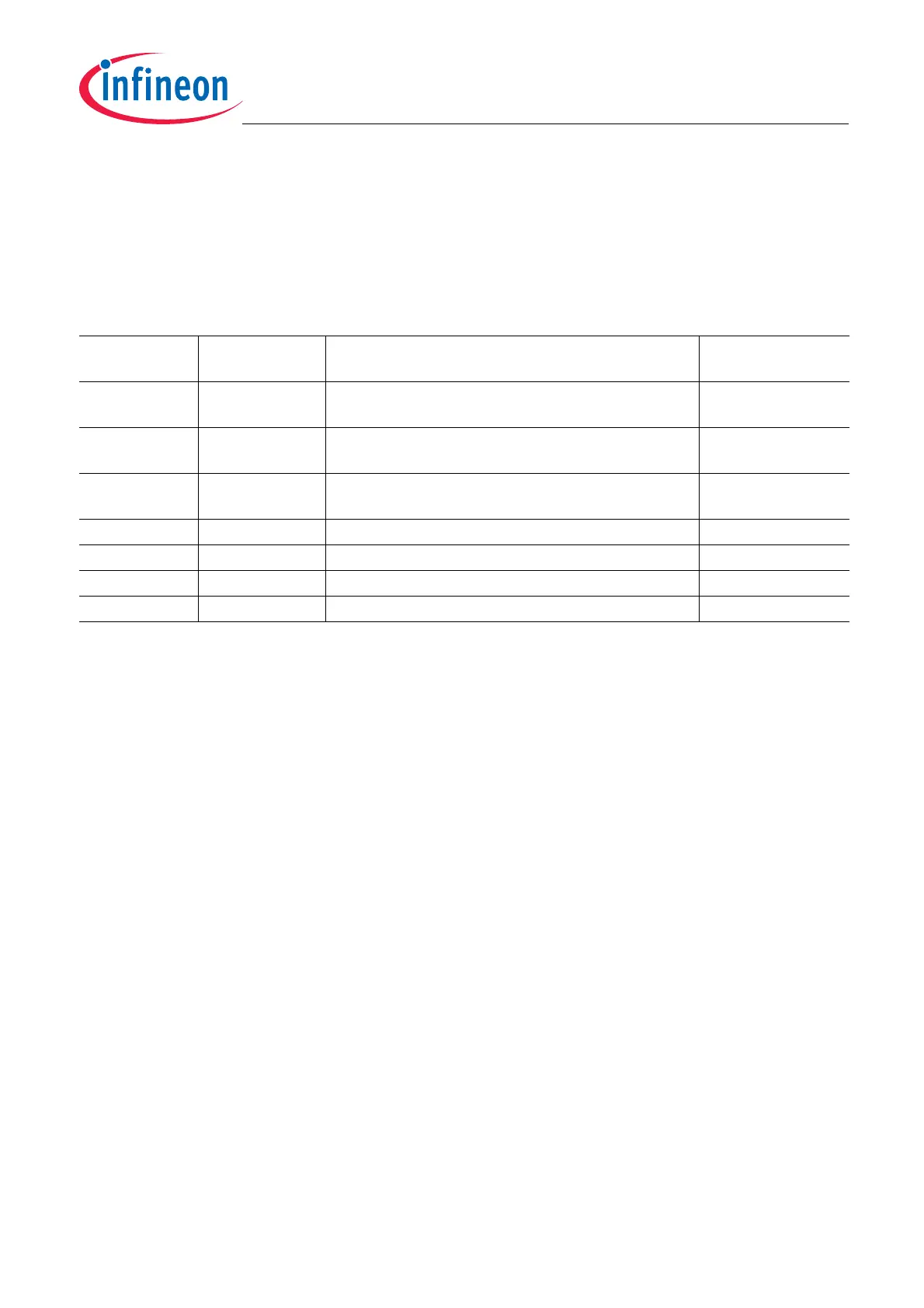

2.10 Load and Store Instructions

The load (LD.x) and store (ST.x) instructions move data between registers and memory using seven addressing

modes (Table 2-3).

The addressing mode determines the effective byte address for the load or store instruction and any update of the

base pointer address register.

2.10.1 Load/Store Basic Data Types

The TriCore architecture defines loads and stores for the basic data types (corresponding to bytes, half-words,

words, and double-words), as well as for signed fractions and addresses.

Note that when the data loaded from memory is smaller than the destination register (i.e. 8-bit and 16-bit

quantities), the data is loaded into the least-significant bits of the register (except for fractions which are loaded

into the most-significant bits of a register), and the remaining register bits are sign or zero-extended to 32-bits,

depending on the particular instruction.

Table 2-3 Addressing Modes

Addressing

Mode

Syntax Effective Address Instruction Format

Absolute Constant {offset 18[17:14], 14’b00000000000000, offset

18[13:0]}

ABS

Base + Short

Offset

A[n]offset A[n]+sign_ext(offset10) BO

Base + Long

Offset

A[n]offset A[n]+sign_ext(offset16) BOL

Pre-Increment +A[n]offset A[n]+sign_ext(offset10) BO

Post-Increment A[n+]offset A[n] BO

Circular A[n] / A[n+1+c] A[n]+A[n+1][15:0] (n is even) BO

Bit-reverse A[n] / A[n+r] A[n]+A[n+1][15:0] (n is even) BO

Loading...

Loading...