TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-76

CMPSWAP.W

Compare and Swap

Description

The CMPSWAP.W instruction conditionally swaps the data register D[a] and the contents of the memory word

specified by the addressing mode.

If the contents of the memory word specified by the addressing mode is equal to the contents of register D[a+1]

then swap the contents of the memory word with the register D[a]. Register D[a] is unconditionally updated with

the contents of the memory word specified by the addressing mode.

CMPSWAP.WA[b], off10, E[a] (BO)(Base + Short Offset Addressing Mode)

EA = A[b] + sign_ext(off10);

tmp = M(EA, word);

M(EA, word) = (tmp == D[a+1]) ? D[a] : tmp;

D[a] = tmp;

CMPSWAP.WP[b], E[a] (BO)(Bit-reverse Addressing Mode)

index = zero_ext(A[b+1][15:0]);

incr = zero_ext(A[b+1][31:16]);

EA = A[b] + index;

tmp = M(EA, word);

M(EA, word) = (tmp == D[a+1]) ? D[a] : tmp;

D[a] = tmp;

new_index = reverse16(reverse16(index) + reverse16(incr));

A[b+1] = {incr[15:0], new_index[15:0]};

CMPSWAP.WP[b], off10, E[a] (BO)(Circular Addressing Mode)

index = zero_ext(A[b+1][15:0]);

length = zero_ext(A[b+1][31:16]);

EA = A[b] + index;

tmp = M(EA, word);

M(EA, word) = (tmp == D[a+1]) ? D[a] : tmp;

D[a] = tmp;

new_index = index + sign_ext(off10);

new_index = new_index < 0 ? new_index + length : new_index % length;

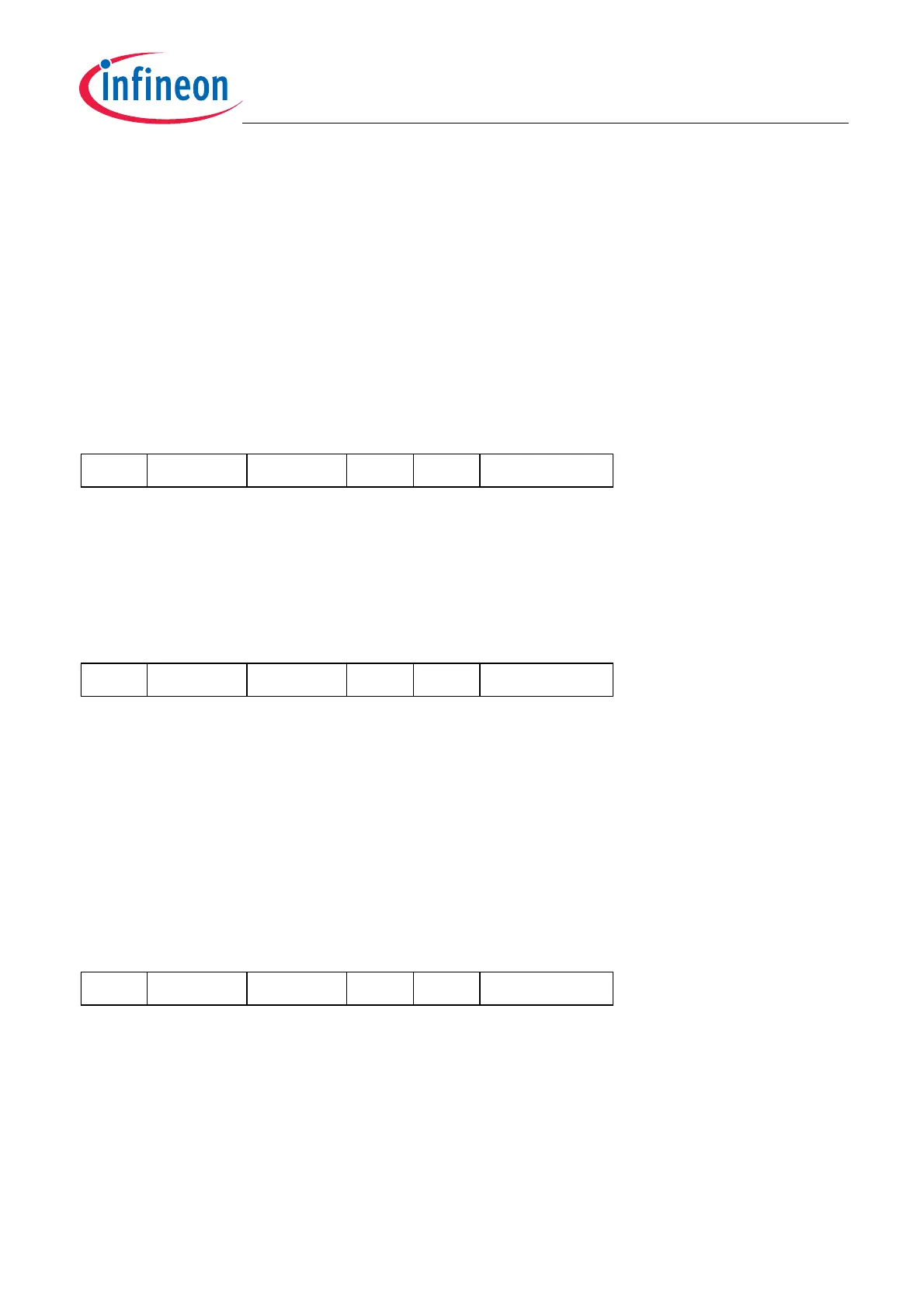

31

off10[9:6]

28 27

23

H

22 21

off10[5:0]

16 15

b

12 11

a

8 7

49

H

0

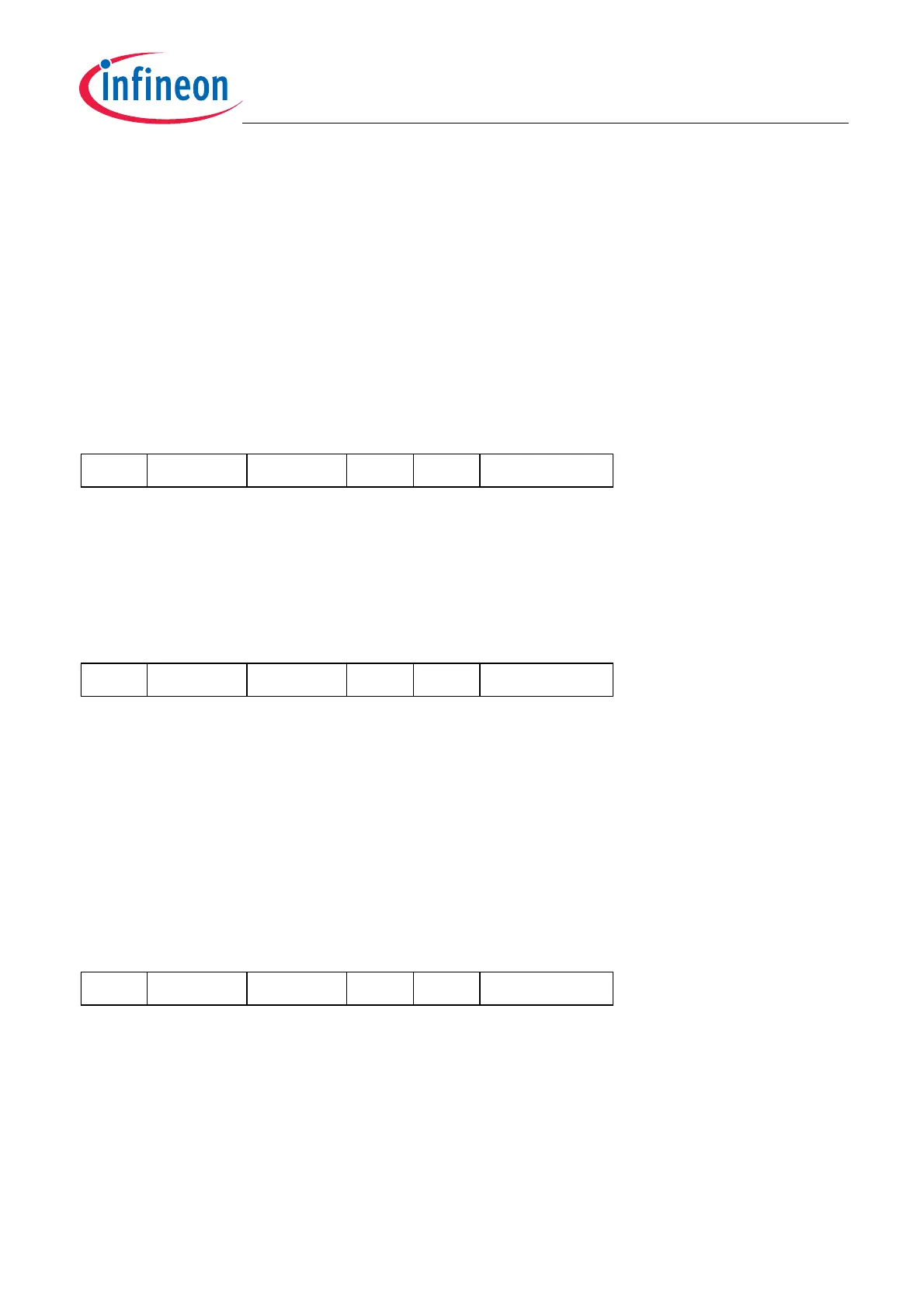

31

-

28 27

03

H

22 21

-

16 15

b

12 11

a

8 7

69

H

0

31

off10[9:6]

28 27

13

H

22 21

off10[5:0]

16 15

b

12 11

a

8 7

69

H

0

Loading...

Loading...