TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-222

MFCR

Move From Core Register

Description

Move the contents of the Core Special Function Register (CSFR), selected by the value const16, to data register

D[c]. The CSFR address is a const16 byte offset from the CSFR base address. It must be word-aligned (the least-

significant two bits equal zero). Nonaligned addresses have an undefined effect.

MFCR can be executed on any privilege level. This instruction may not be used to access GPRs. Attempting to

access a GPR with this instruction will return an undefined value.

MFCRD[c], const16 (RLC)

D[c] = CR[const16];

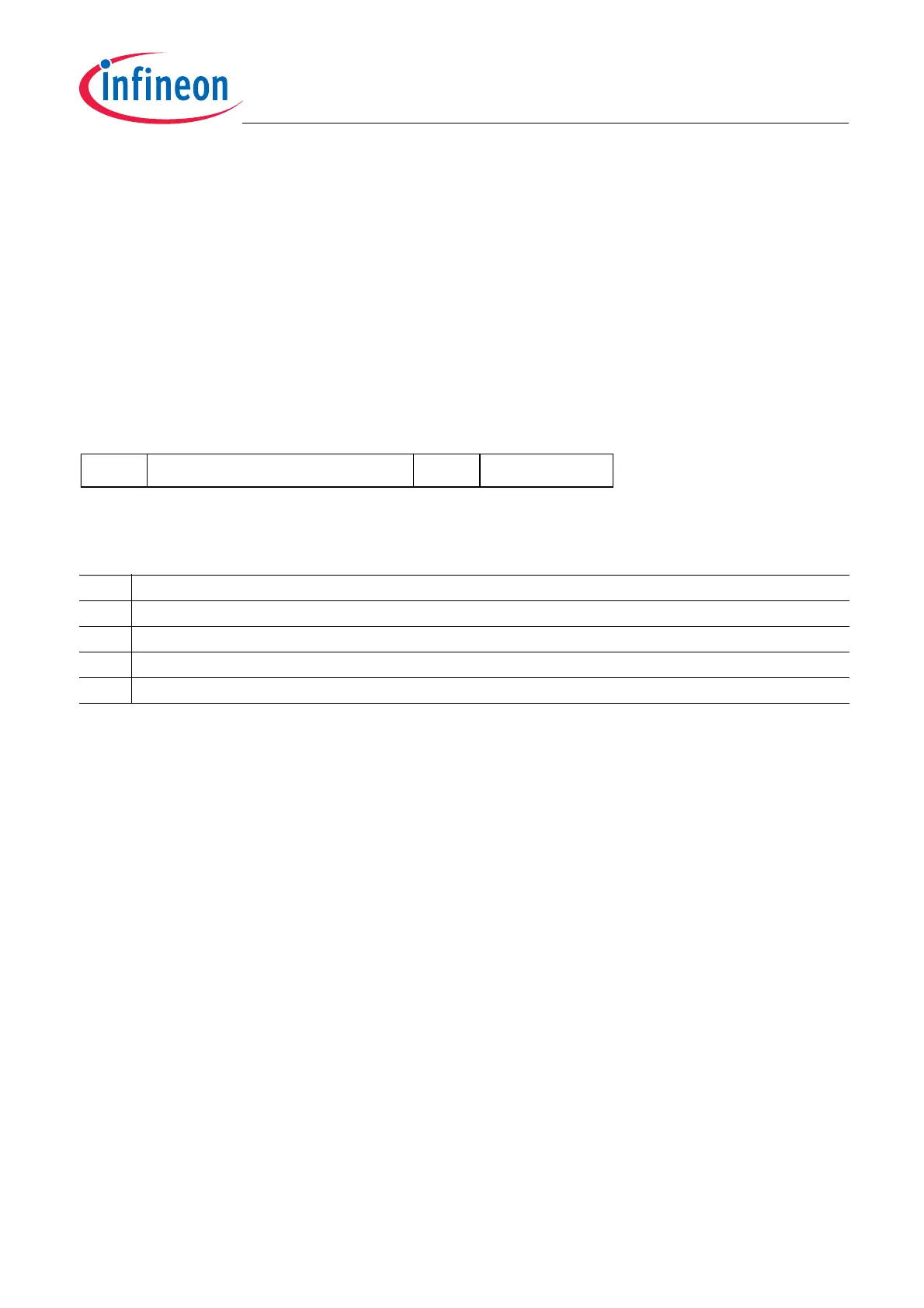

Status Flags

Examples

mfcr d3, fe04

H

See Also

MTCR

C Read by the instruction but not changed.

V Read by the instruction but not changed.

SV Read by the instruction but not changed.

AV Read by the instruction but not changed.

SAV Read by the instruction but not changed.

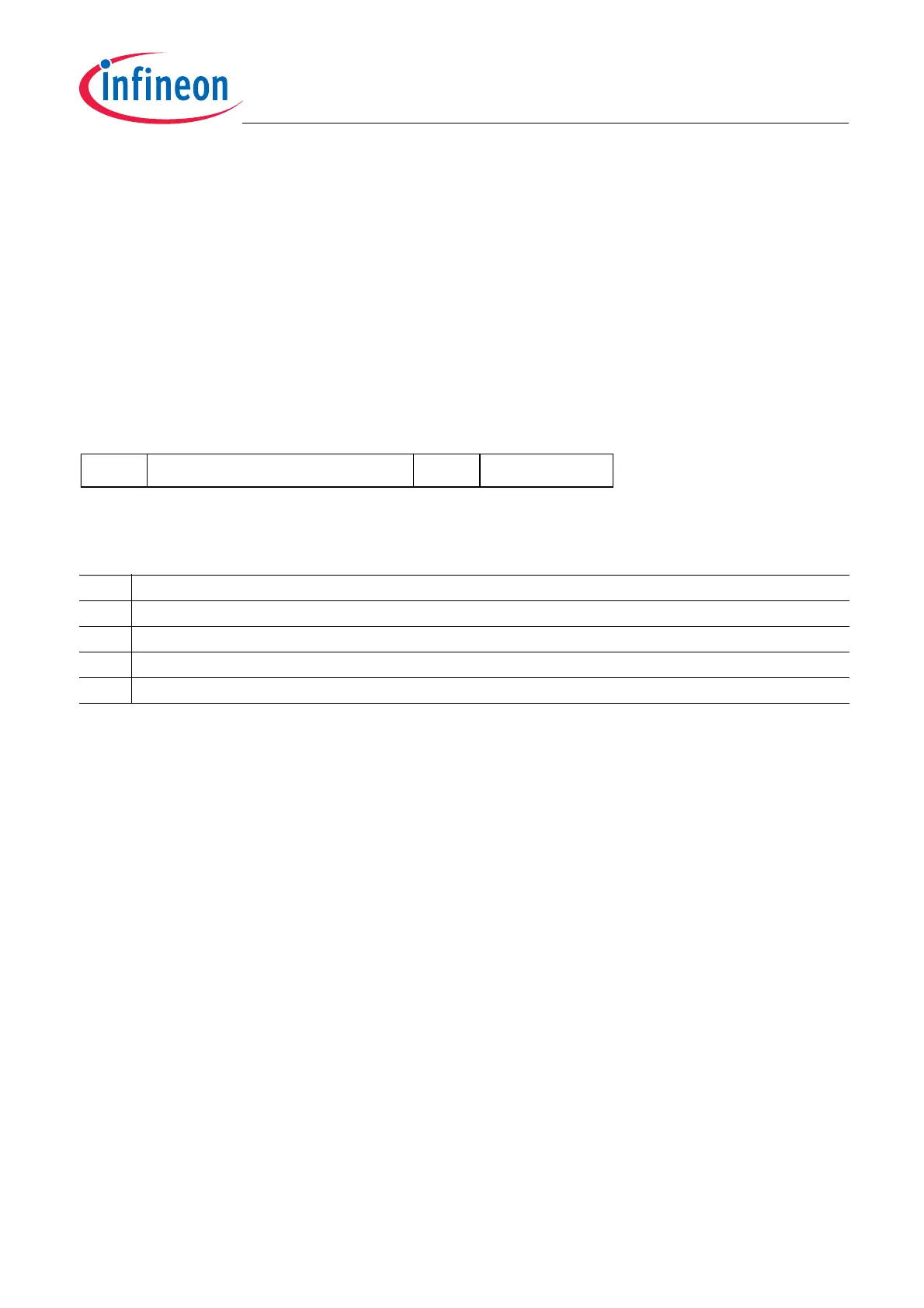

31

c

28 27

const16

12 11

-

8 7

4D

H

0

Loading...

Loading...