TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-312

PARITY

Parity

Description

Compute the four byte parity bits of data register D[a]. Put each byte parity bit into every 8th bit of the data register

D[c] and then clear the remaining bits of D[c]. A byte parity bit is set to one if the number of ones in a byte is an

odd number.

PARITYD[c], D[a] (RR)

D[c][31:24] = {7'b0, D[a][31] ^ D[a][30] ^ D[a][29] ^ D[a][28] ^ D[a][27] ^ D[a][26] ^ D[a][25] ^ D[a][24]};

D[c][23:16] = {7'b0, D[a][23] ^ D[a][22] ^ D[a][21] ^ D[a][20] ^ D[a][19] ^ D[a][18] ^ D[a][17] ^ D[a][16]};

D[c][15:8] = {7'b0, D[a][15] ^ D[a][14] ^ D[a][13] ^ D[a][12] ^ D[a][11] ^ D[a][10] ^ D[a][9] ^ D[a][8]};

D[c][7:0] = {7'b0, D[a][7] ^ D[a][6] ^ D[a][5] ^ D[a][4] ^ D[a][3] ^ D[a][2] ^ D[a][1] ^ D[a][0]};

Status Flags

Examples

parity d3, d5

See Also

-

C Not set by this instruction.

V Not set by this instruction.

SV Not set by this instruction.

AV Not set by this instruction.

SAV Not set by this instruction.

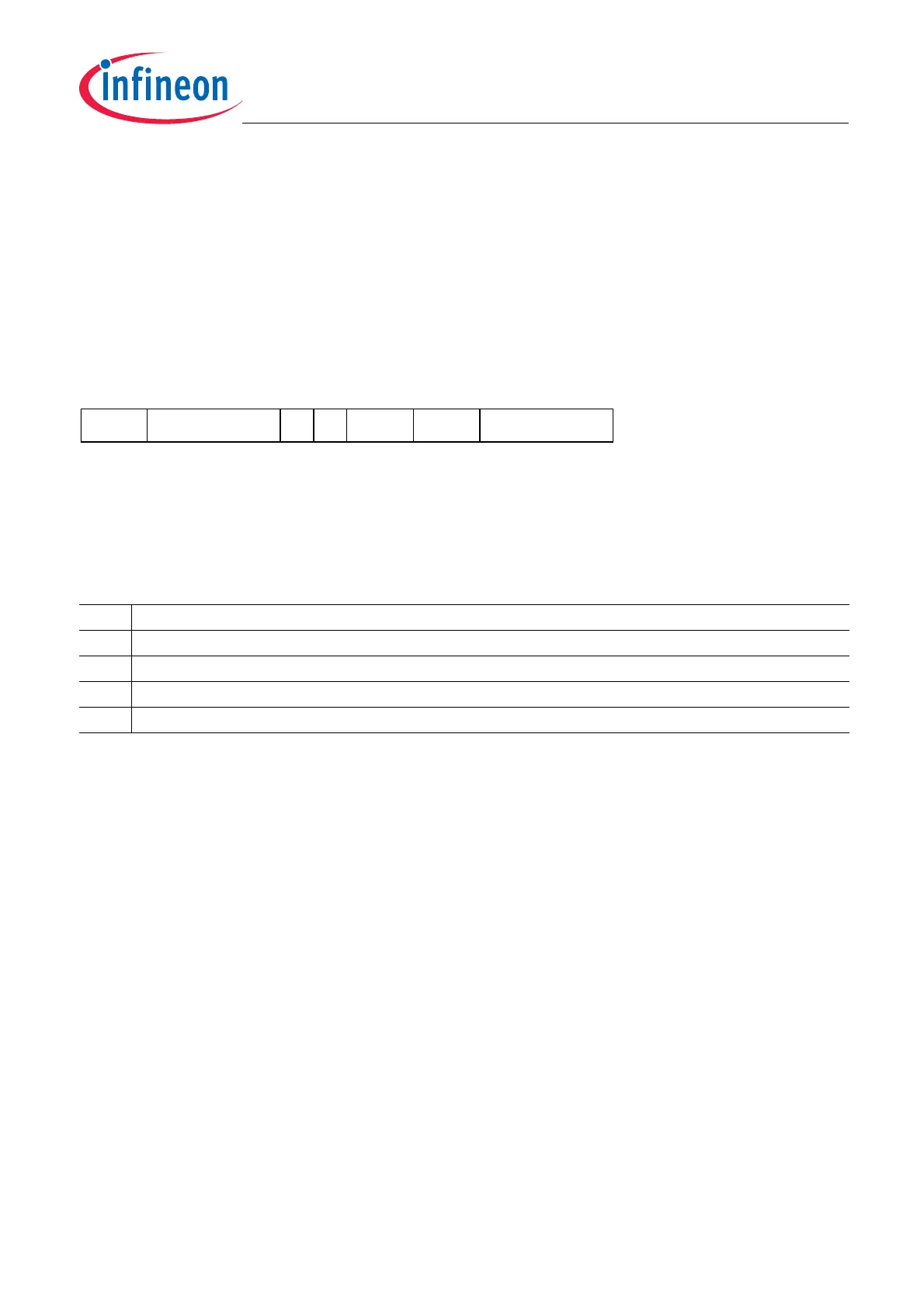

31

c

28 27

02

H

20 19

-

18 17

0

H

16 15

-

12 11

a

8 7

4B

H

0

Loading...

Loading...