TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set Overview

V1.0 2013-07

User Manual (Volume 2) 2-5

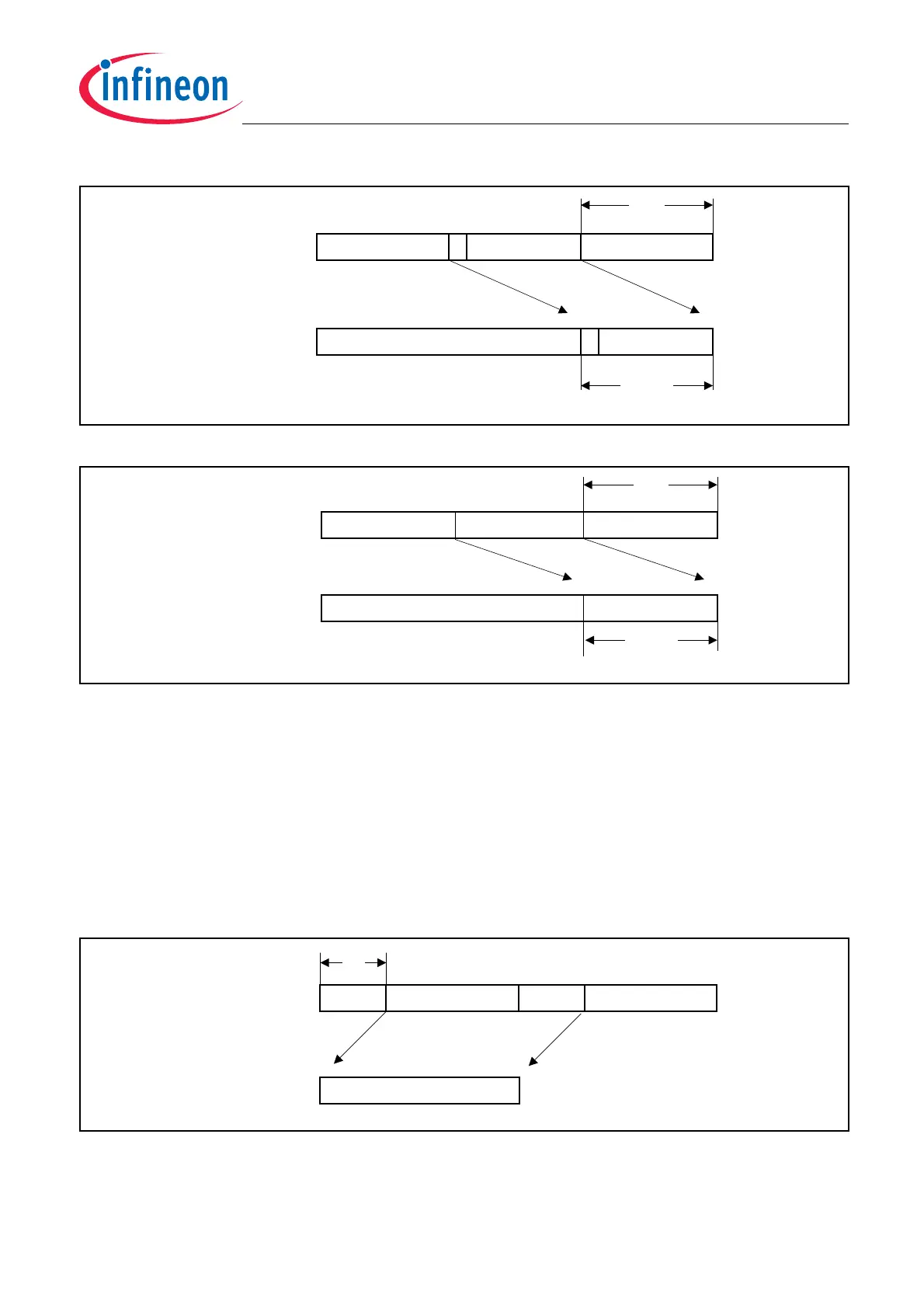

Figure 2-2 EXTR Operation

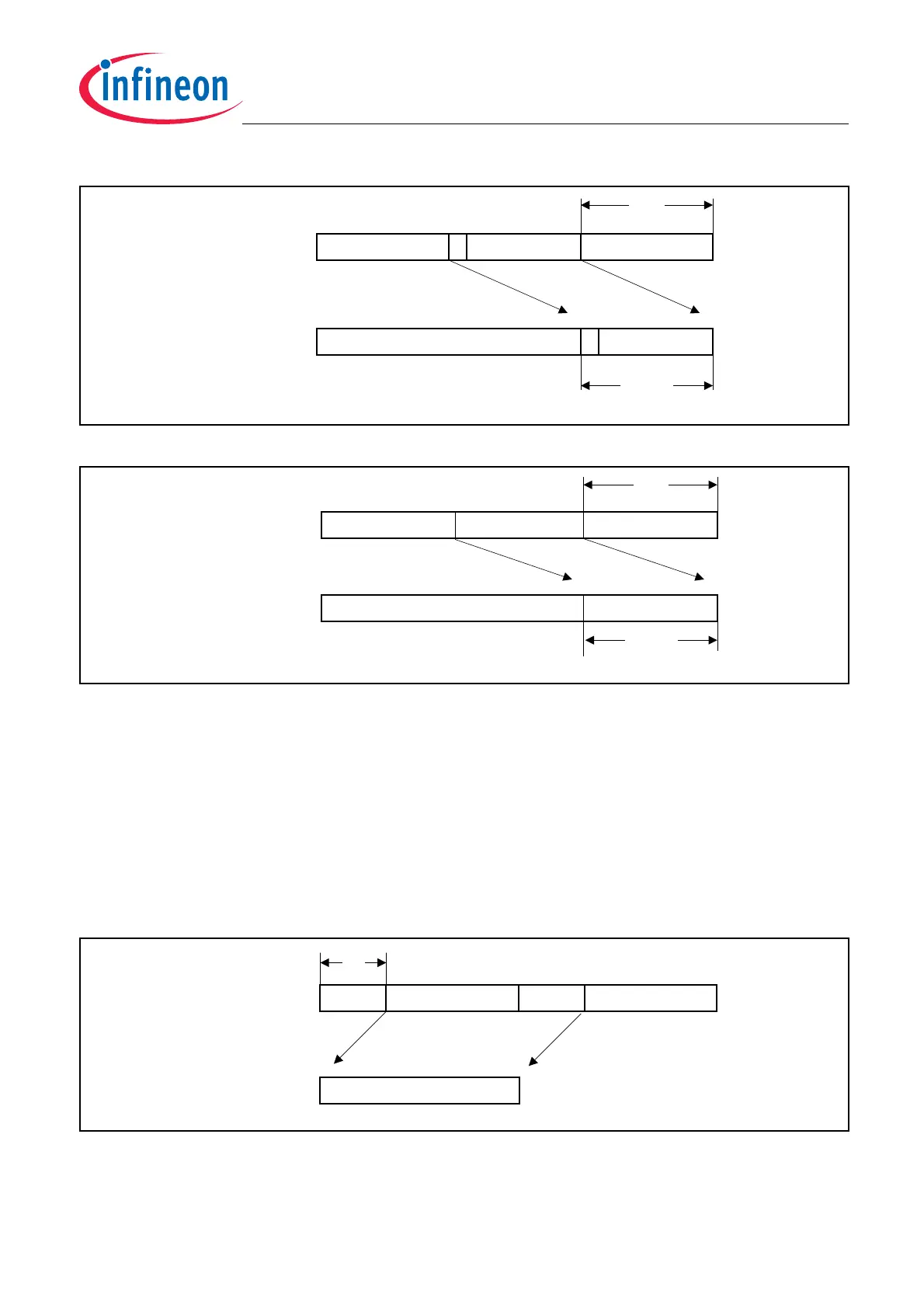

Figure 2-3 EXTR.U Operation

DEXTR

The DEXTR instruction concatenates two data register sources to form a 64-bit value from which 32 consecutive

bits are extracted. The operation can be thought of as a left shift by pos bits, followed by the truncation of the least-

significant 32-bits of the result. The value of pos is contained in a data register, or is an immediate value in the

instruction.

The DEXTR instruction can be used to normalize the result of a DSP filter accumulation in which a 64-bit

accumulator is used with several guard bits. The value of pos can be determined by using the CLS (Count Leading

Signs) instruction. The DEXTR instruction can also be used to perform a multi-bit rotation by using the same

source register for both of the sources (that are concatenated).

Figure 2-4 DEXTR Operation

TC1046B

Source Registers

31 0

S

Destination Register

31 0

Sign Fill

Width

Pos

S

S

TC1045B

Source Registers

31 0

Destination Register

31 0

Zero fill

Width

Pos

0

TC1047B

Source Registers

63

0

Destination Register

31

0

Pos

32 31

Loading...

Loading...