TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-338

SH.AND.T

Accumulating Shift-AND

SH.ANDN.T

Accumulating Shift-AND-Not

SH.NAND.T

Accumulating Shift-NAND

SH.NOR.T

Accumulating Shift-NOR

SH.OR.T

Accumulating Shift-OR

SH.ORN.T

Accumulating Shift-OR-Not

SH.XNOR.T

Accumulating Shift-XNOR

SH.XOR.T

Accumulating Shift-XOR

Description

Left shift D[c] by one. The bit shifted out is discarded. Compute the logical operation (AND, ANDN, NAND, NOR,

OR, ORN, XNOR or XOR) of the value of bit pos1 of data register D[a], and bit pos2 of D[b]. Put the result in D[c][0].

SH.AND.TD[c], D[a], pos1, D[b], pos2 (BIT)

D[c] = {D[c][30:0], (D[a][pos1] AND D[b][pos2])};

SH.ANDN.TD[c], D[a], pos1, D[b], pos2 (BIT)

D[c] = {D[c][30:0], (D[a][pos1] AND !(D[b][pos2]))};

SH.NAND.TD[c], D[a], pos1, D[b], pos2 (BIT)

D[c] = {D[c][30:0], !(D[a][pos1] AND D[b][pos2])};

SH.NOR.TD[c], D[a], pos1, D[b], pos2 (BIT)

D[c] = {D[c][30:0], !(D[a][pos1] OR D[b][pos2])};

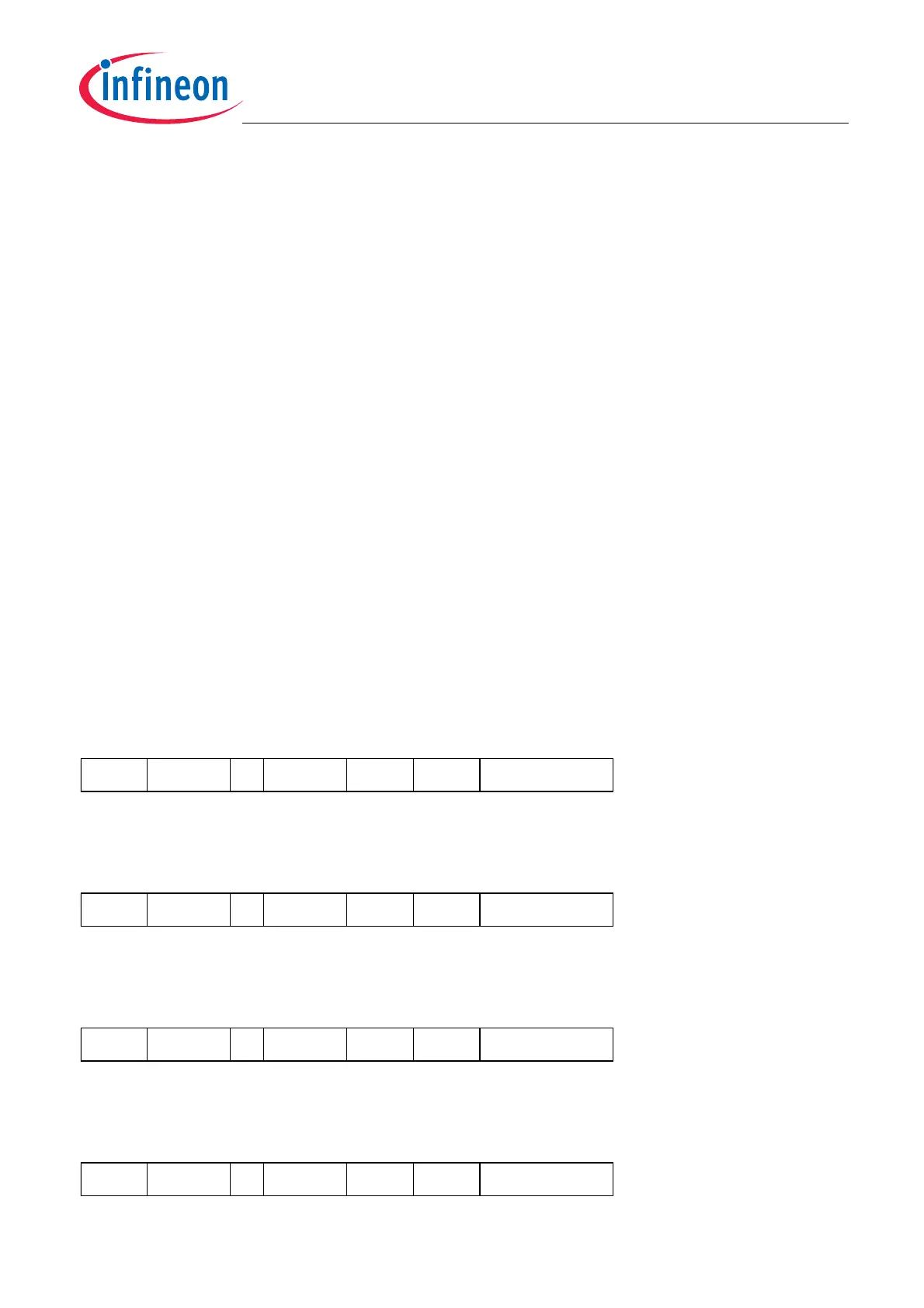

31

c

28 27

pos2

23 22

00

H

21 20

pos1

16 15

b

12 11

a

8 7

27

H

0

31

c

28 27

pos2

23 22

03

H

21 20

pos1

16 15

b

12 11

a

8 7

27

H

0

31

c

28 27

pos2

23 22

00

H

21 20

pos1

16 15

b

12 11

a

8 7

A7

H

0

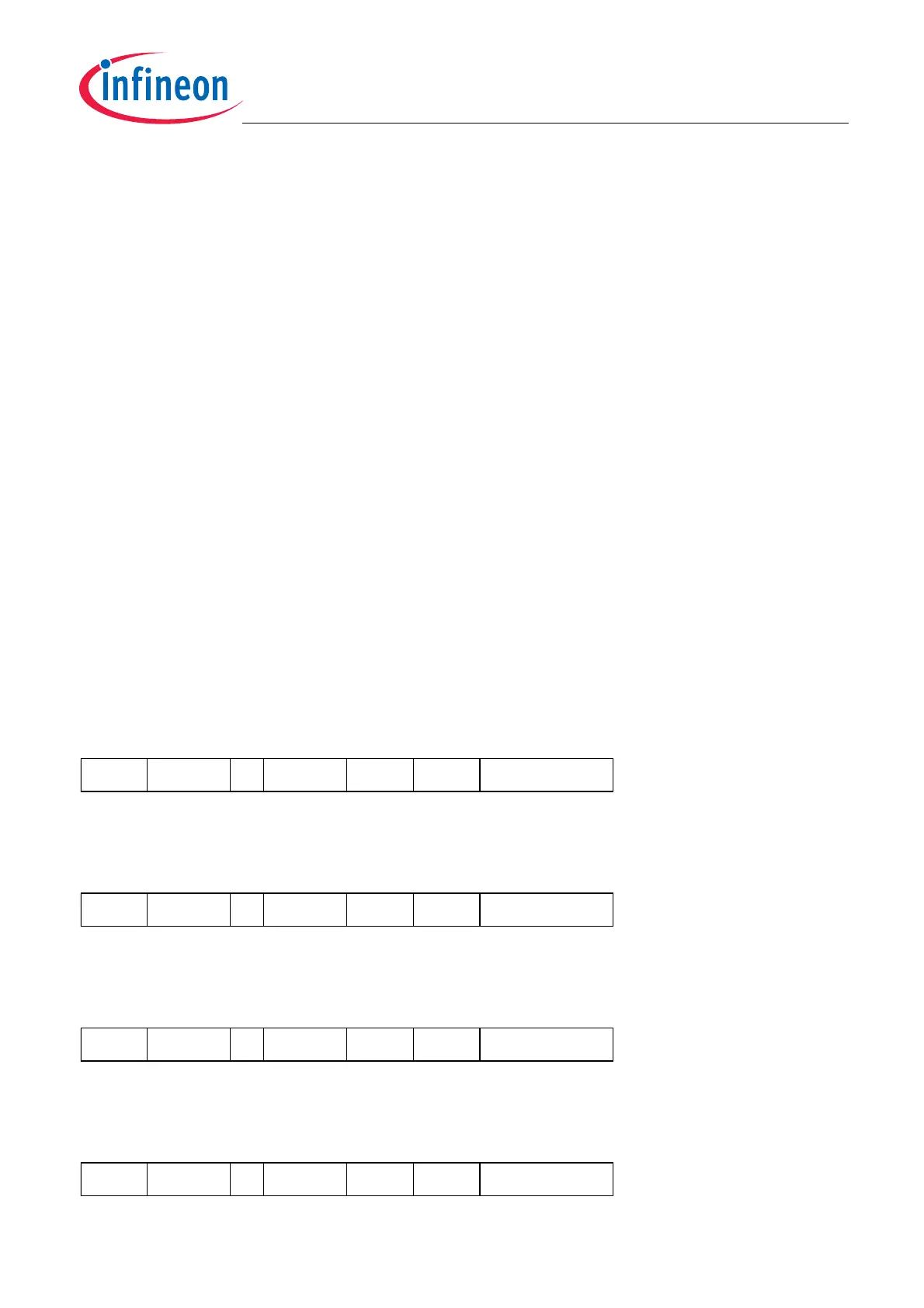

31

c

28 27

pos2

23 22

02

H

21 20

pos1

16 15

b

12 11

a

8 7

27

H

0

Loading...

Loading...