TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-87

DIV

Divide

DIV.U

Divide Unsigned

Description

Divide the contents of register D[a] by the contents of register D[b]. Put the resulting quotient in E[c][31:0] and the

remainder in E[c][63:32].

The operands and results are treated as signed 32-bit integers for the DIV instruction and as unsigned 32-bit

integers for the DIV.U instruction.

Overflow occurs if the divisor (D[b]) is zero. For DIV, Overflow also occurs if the dividend (D[a]) is the maximum

negative number and the divisor is minus 1.

DIVE[c], D[a], D[b] (RR)

dividend = D[a];

divisor = D[b];

if (divisor == 0) then {

if (dividend >= 0) then {

quotient = 0x7fffffff;

remainder = 0x00000000;

} else {

quotient = 0x80000000;

remainder = 0x00000000;

}

} else if ((divisor == 0xffffffff) AND (dividend == 0x80000000)) then {

quotient = 0x7fffffff;

remainder = 0x00000000;

} else {

remainder = dividend % divisor

quotient = (dividend - remainder)/divisor

}

E[c][31:0] = quotient;

E[c][63:32] = remainder;

DIV.UE[c], D[a], D[b] (RR)

dividend = D[a];

divisor = D[b];

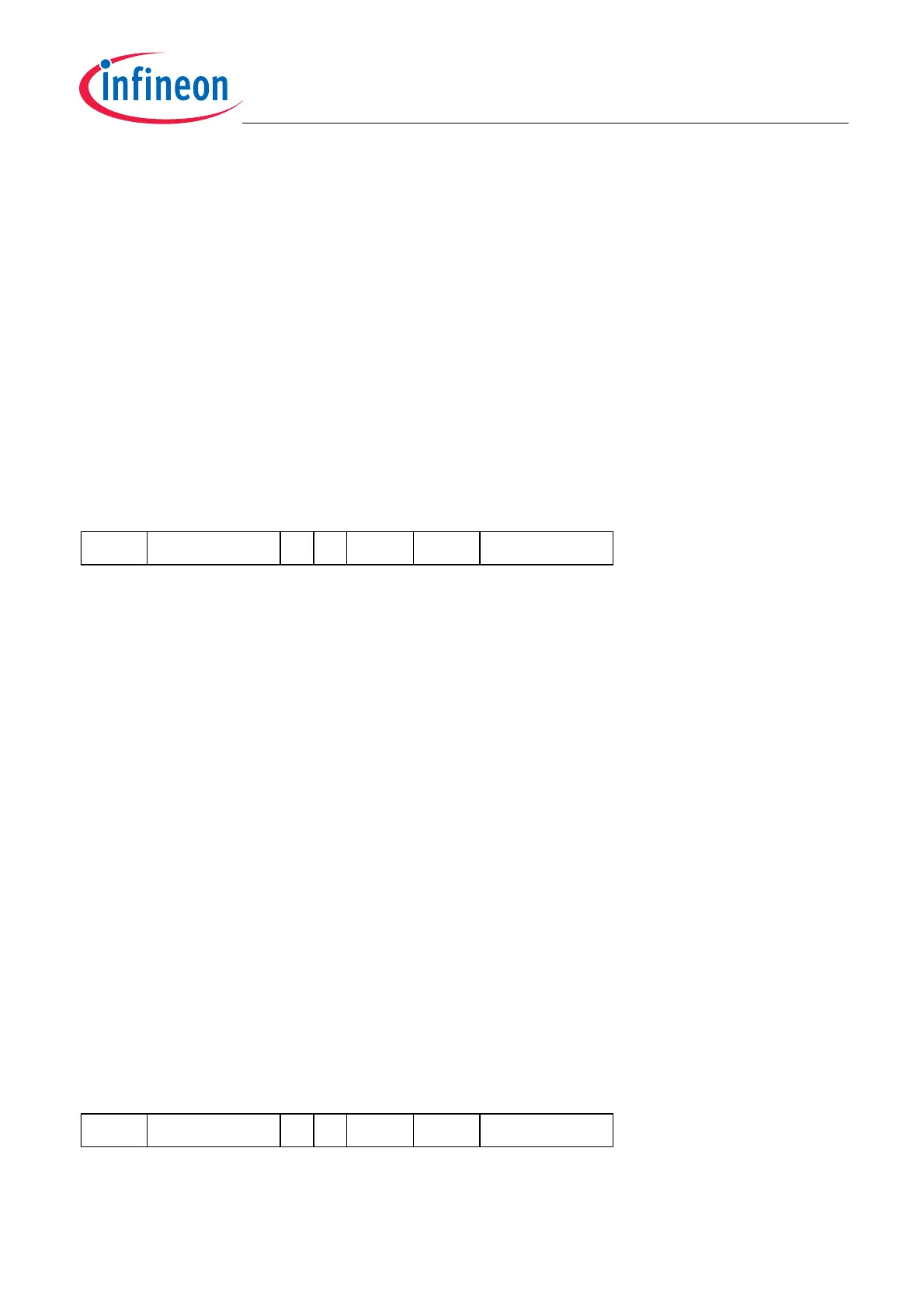

31

c

28 27

20

H

20 19

-

18 17

1

H

16 15

b

12 11

a

8 7

4B

H

0

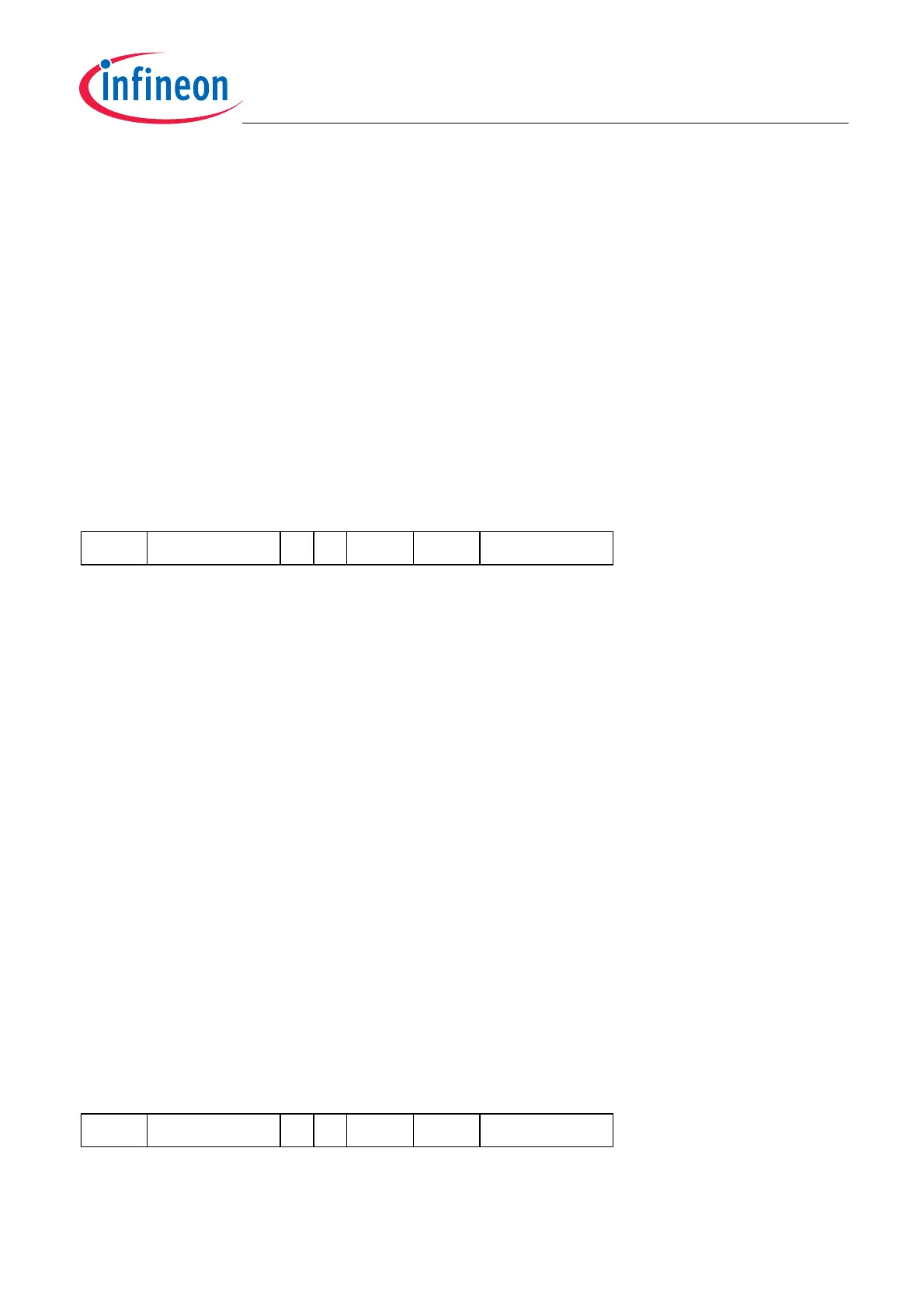

31

c

28 27

21

H

20 19

-

18 17

1

H

16 15

b

12 11

a

8 7

4B

H

0

Loading...

Loading...