TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set Information

V1.0 2013-07

User Manual (Volume 2) 1-5

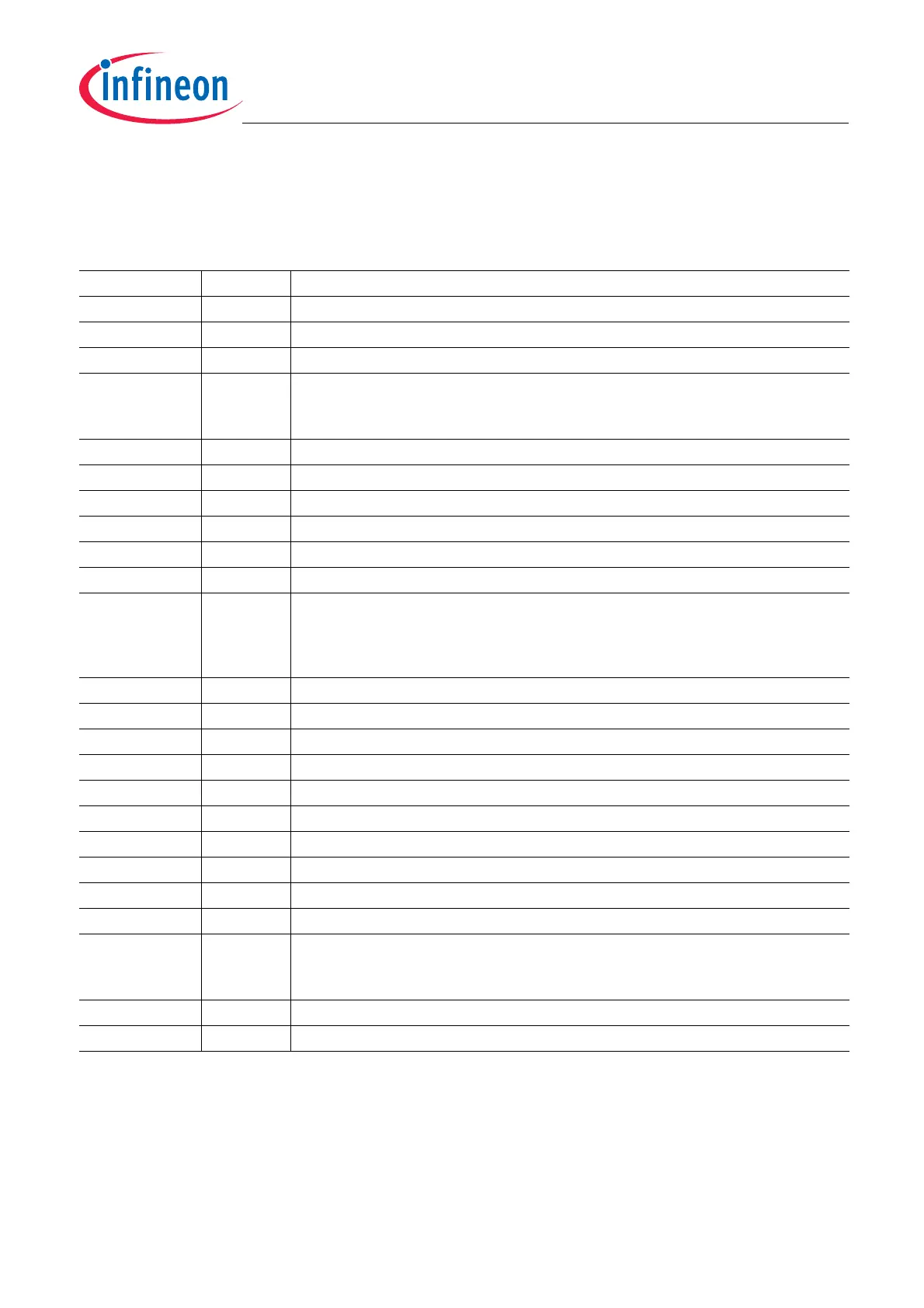

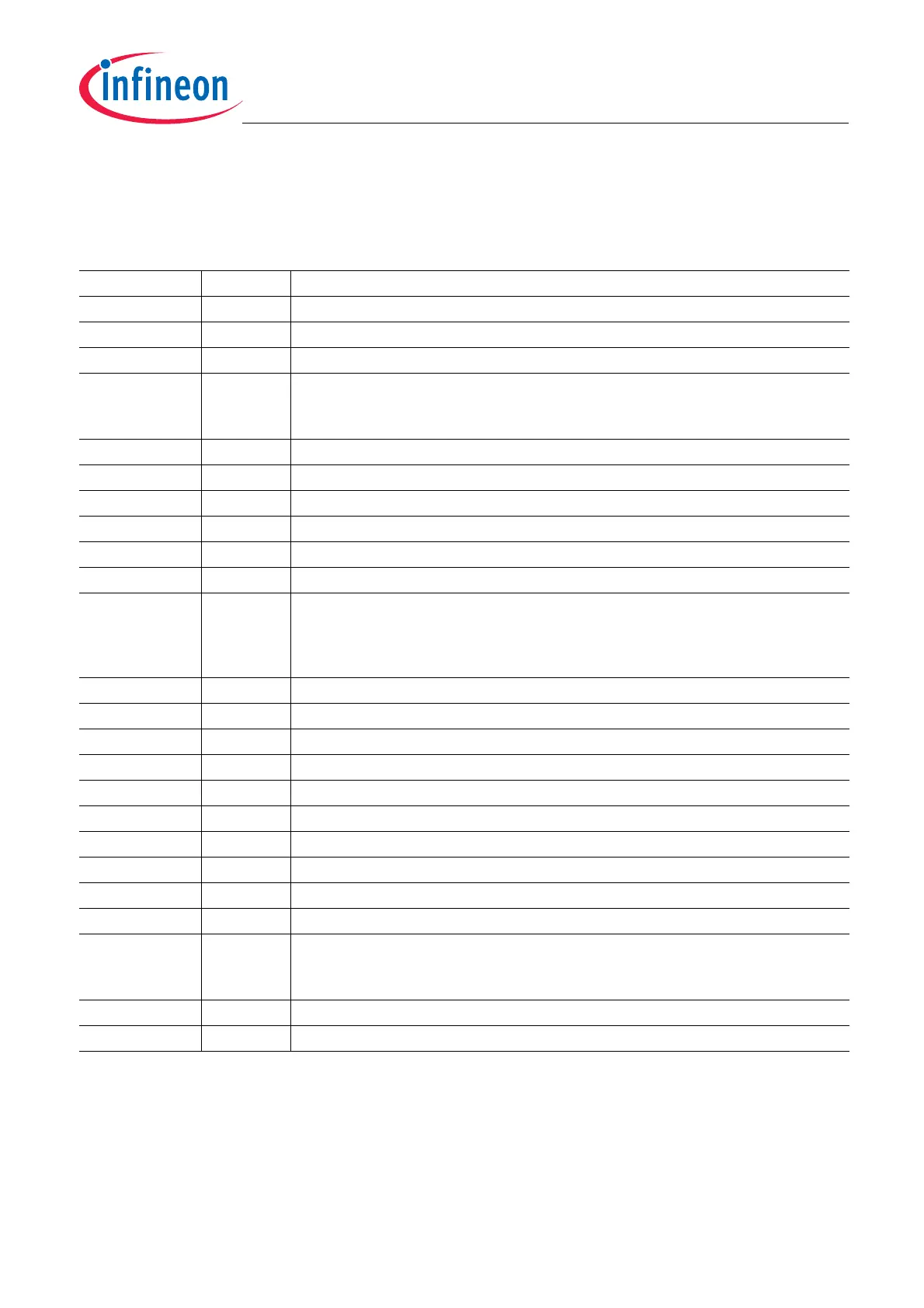

1.2.3 Opcode Field Definitions

Table 1-7 Opcode Field Definitions

Name Width Definition

s1 4 Source register(s) one

s2 4 Source register(s) number two

s3 4 Source register(s) number three

d 4 Destination register

For a register pair (E), the coding follows the register number:

E[0] = 0000

B

, E[2] = 0010

B

, E[4] = 0100

B

, and so on.

b1Bit value

bpos3 3 Bit position in a byte

pos 5 Bit position in a register

pos1 5 Bit position in a register

pos2 5 Bit position in a register

width 5 Bit position in a register

n2

• Multiplication result shift value (only 00

B

and 01

B

are valid).

• Address shift value in add scale.

• Default to zero in all other operations using the RR format.

• Coprocessor number for coprocessor instructions.

const4 4 4-bit constant

const9 9 9-bit constant

const16 16 16-bit constant

disp4 4 4-bit displacement

disp8 8 8-bit displacement

disp15 15 15-bit displacement

disp24 24 24-bit displacement

off4 4 4-bit offset

off10 10 10-bit offset

off16 16 16-bit offset

- - Reserved field.

Read value is undefined; should be written with zero (0).

Must be set to zero (0) to allow for future compatibility.

op1 Primary Opcode

op2 Secondary Opcode

Loading...

Loading...