TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-402

DIV.F

Divide Float

Description

Divides the contents of data register D[a] by the contents of data register D[b] and put the result in data register

D[c]. The operands and result are single-precision IEEE-754-1985 floating-point numbers. If either operand is a

NaN (quiet or signalling), then the return result will be the quiet NaN 7FC00000

H

.

DIV.FD[c], D[a], D[b] (RR)

arg_a = denorm_to_zero(f_real(D[a]);

arg_b = denorm_to_zero(f_real(D[b]);

if(is_nan(D[a]) OR is_nan(D[b])) then result = QUIET_NAN;

else if(is_inf(D[a]) AND is_inf(D[b])) then result = DIV_NAN;

else if(is_zero(D[a]) AND is_zero(D[b])) then result = DIV_NAN;

else {

precise_result = divide(arg_a,arg_b);

normal_result = denorm_to_zero(precise_result);

rounded_result = ieee754_round(normal_result, PSW.RM);

result = ieee754_32bit_format(rounded_result);

}

D[c] = result[31:0];

Exception Flags

Examples

div.f d3, d1, d2

See Also

-

FS if(set_FI OR set_FV OR set_FZ OR set_FU OR set_FX) then PSW.FS = 1 else PSW.FS = 0;

FI if(is_s_nan(D[a]) OR is_s_nan(D[b]) OR (D[c] == DIV_NAN)) then set_FI = 1 else set_FI = 0;

if(set_FI) then PSW.FI = 1;

FV if(rounded_result >= 2

128

) then set_FV = 1 else set_FV = 0;

if(set_FV) then PSW.FV = 1;

FZ if(is_zero(D[b]) AND !(is_inf(D[a])) then set_FZ = 1 else set_FZ = 0;

if(set_FZ) then PSW.FZ = 1;

FU if(fp_abs(precise_result) < 2

-126

) then set_FU = 1 else set_FU = 0;

if(set_FU) then PSW.FU = 1;

FX if(precise_result != f_real(result)) then set_FX = 1 else set_FX = 0;

if(set_FX AND !set_FI AND !set_FZ) then PSW.FX = 1;

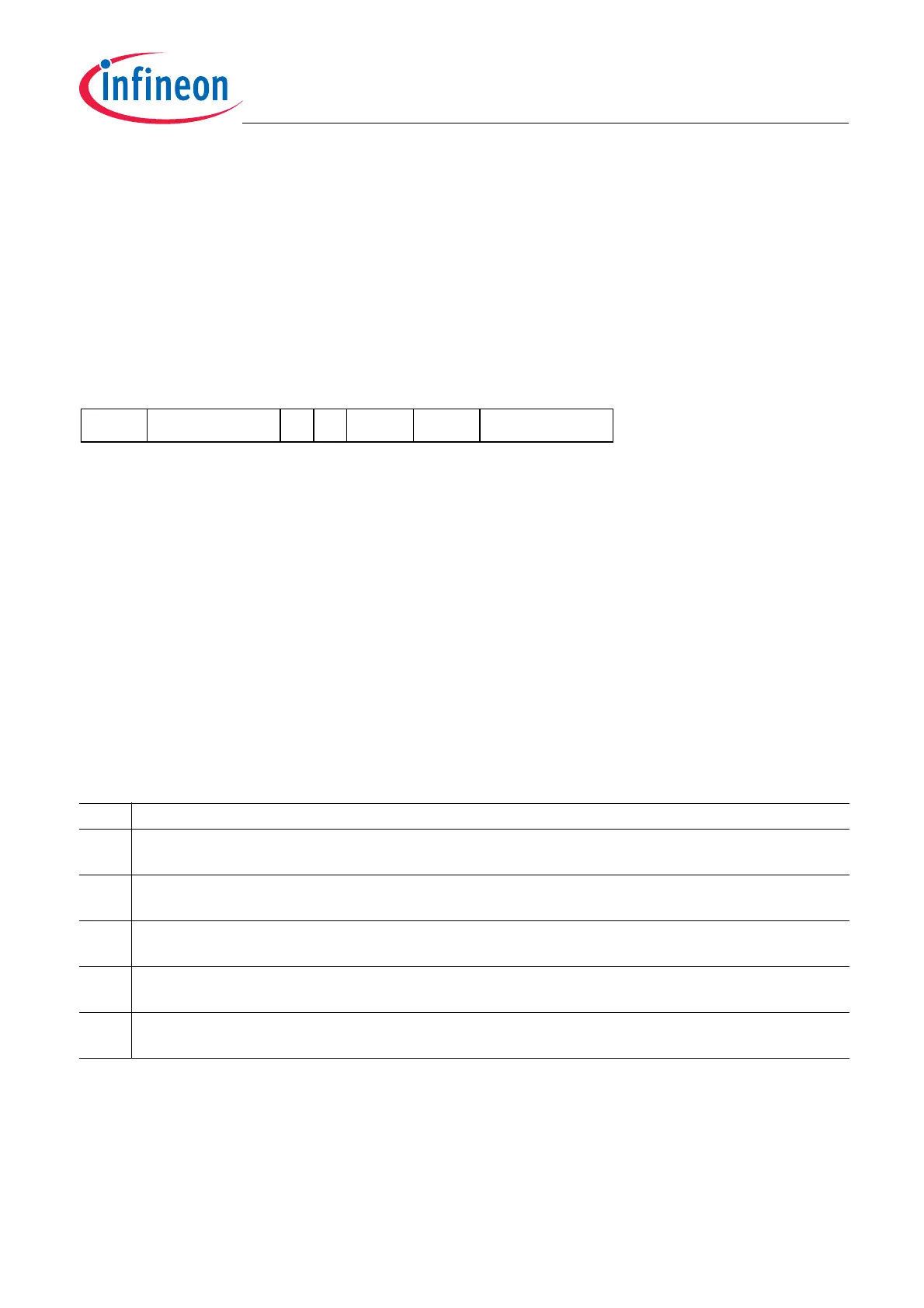

31

c

28 27

05

H

20 19

-

18 17

1

H

16 15

b

12 11

a

8 7

4B

H

0

Loading...

Loading...