TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set Information

V1.0 2013-07

User Manual (Volume 2) 1-6

1.3 Instruction Operation Syntax

The operation of each instruction is described using a ‘C-like’ Register Transfer Level (RTL) notation.

Notes

1. The numbering of bits begins with bit zero, which is the least-significant bit of the word.

2. All intermediate 'result' values are assumed to have infinite precision unless otherwise indicated.

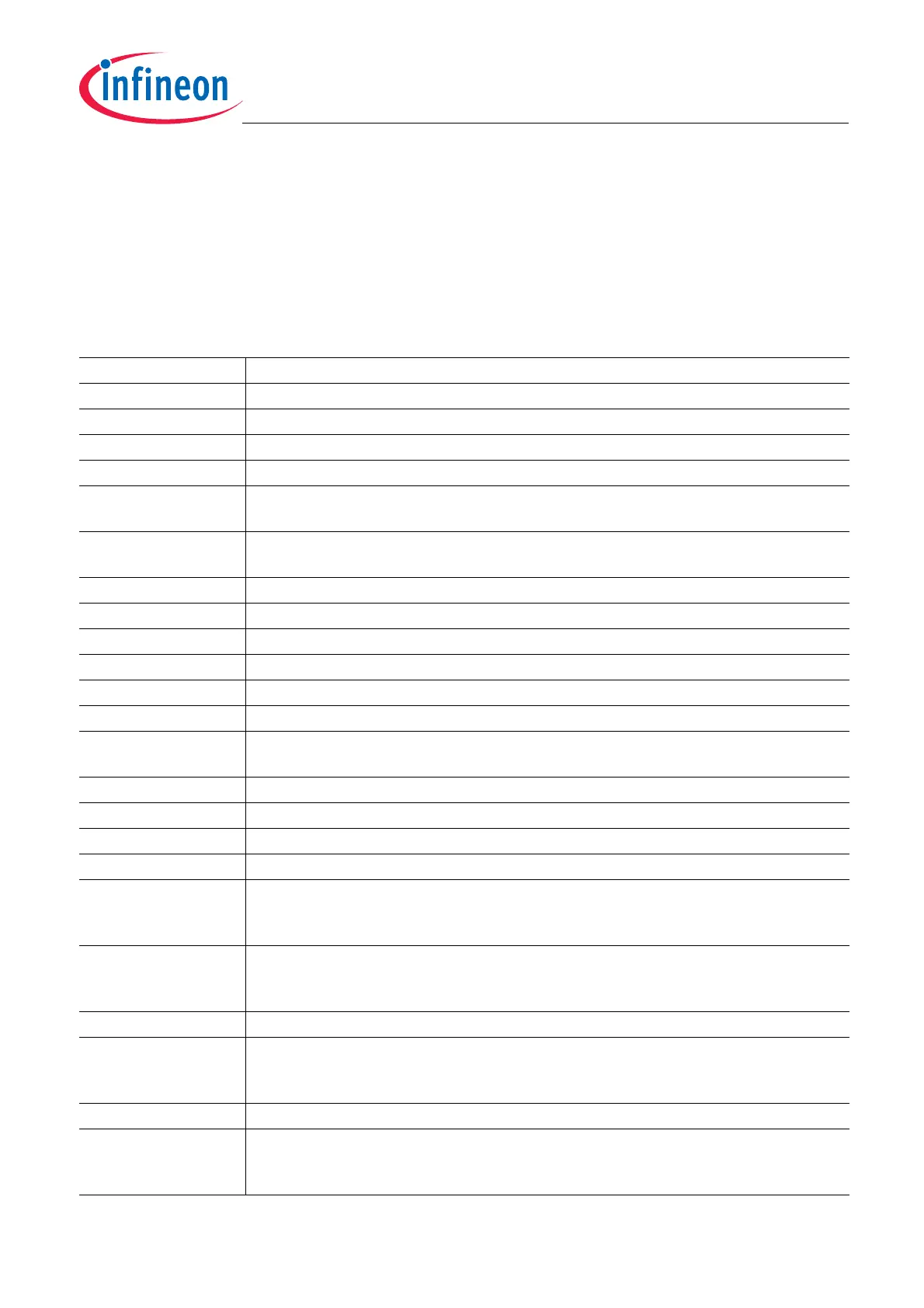

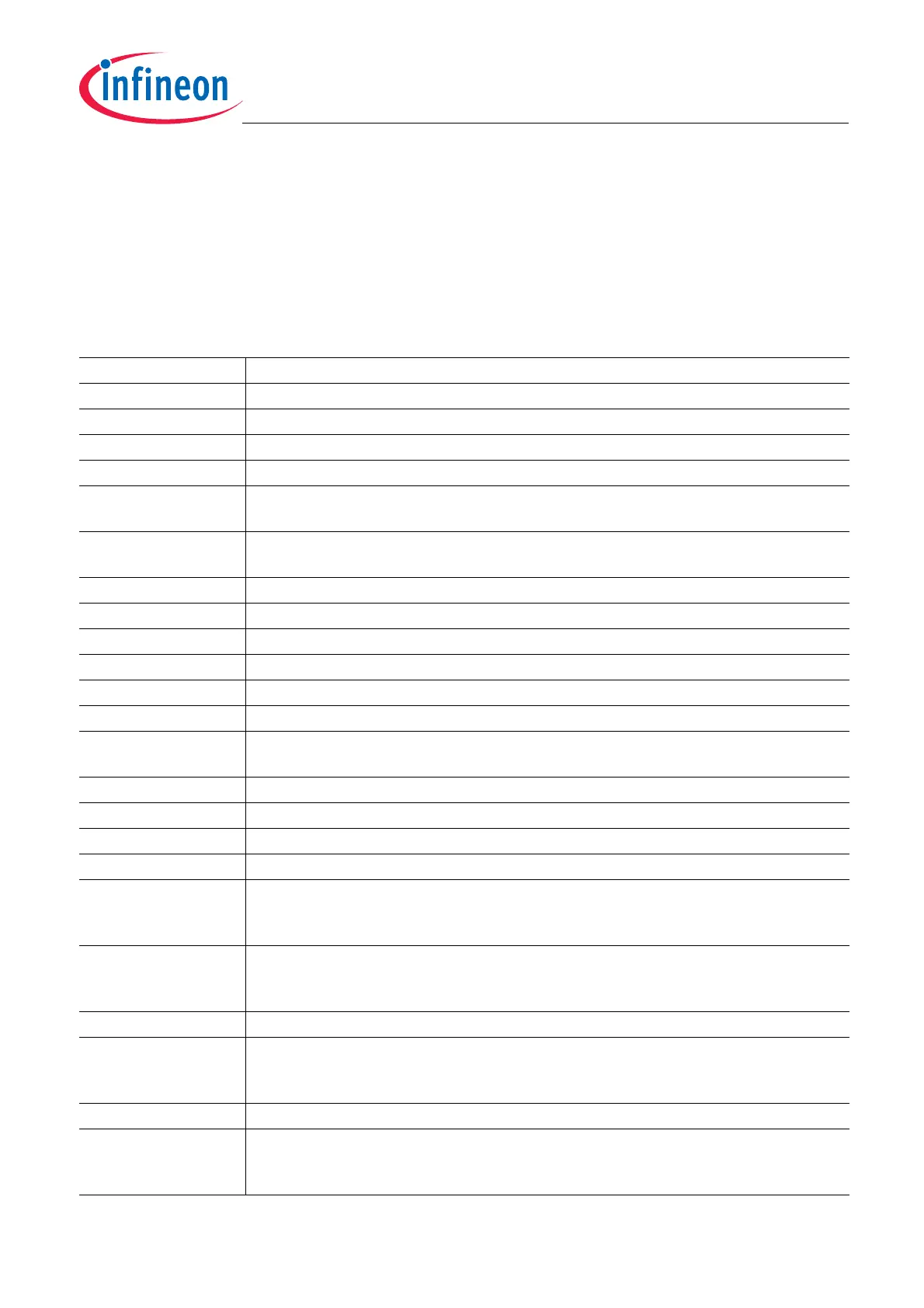

Table 1-8 RTL Syntax

Syntax Definition

bpos3 Bit position

const’n’ Constant value of ‘n’bits, used as instruction operand

disp’n’ Displacement value of ‘n’ bits, used to form the effective address in branch instructions

(expression)[p] A single bit, wiht ordinal index ‘p’ in the bit field ‘expression’

n’bx Constant bit string, where ‘n’ is the number of bits in the constant and ‘x’ is the constant

in binary. For example; 2’b11

n’hx Constant bit string, where ‘n’ is the number of bits in the constant and ‘x’ is the constant

in hexadecimal. For example, 16’hFFFF

off’n’ Offset value of ‘n’ bits, used to form the effective address in Load and Store instructions

pos Single bit position

signed A value that can be positive, negative or zero

ssov Saturation on signed overflow

suov Saturation on unsigned overflow

unsigned A value that can be positive or zero

{x,y} A bit string where ‘x’ and ‘y’ are expressions representing a bit or bit field. Any number

of expressions can be concatenated. For example, {x,y,z}

A[n] Address register ‘n’

CR Core Register

D[n] Data register ‘n’

EA Effective Address

E[n] Data register containing a 64-bit value, constructed by pairing two data registers. The

least-significant bit is in the even register D[n], and the most significant bit is in the odd

register D[n+1]

M(EA, data_size) Memory locations beginning at the specified byte location EA, and extending to EA +

data_size - 1.

data_size = byte, half-word, word, , 16-word

<mode> And addressing mode

P[n] Address register containing a 64-bit value, constructed by pairing two address registers.

The least-significant bit is in the even register A[n], and the most significant bit is in the

odd register A[n+1]

PC The address of the instruction in memory

[x:y] Bits y, y+1, ..., x where x>y;

For example D[a][x:y], if x=y then this is a single bit range which is also denoted by [x],

as in D[a][x]. For cases where x<y, this denotes an empty range.

Loading...

Loading...