TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set Overview

V1.0 2013-07

User Manual (Volume 2) 2-12

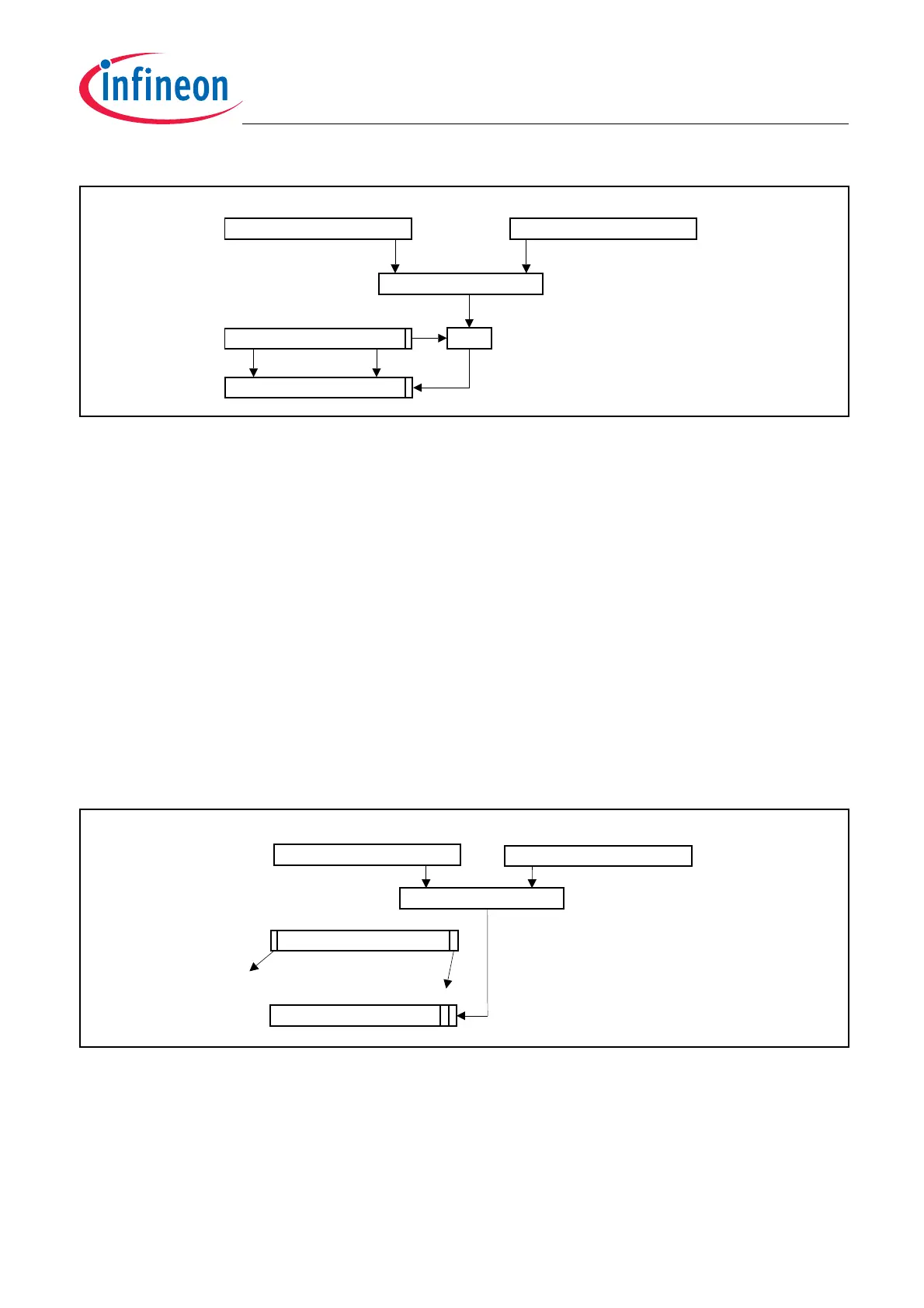

Figure 2-9 Combining LT Comparison with Boolean Operation

The evaluation of the following C expression can be optimized using the combined compare-Boolean operation:

d5 = (d1 < d2) || (d3 == d4);

Assuming all variables are in registers, the following two instructions compute the value in d5:

lt d5, d1, d2; // compute (d1 < d2)

or.eq d5, d3, d4; // or with (d3 == d4)

2.5.3 Compare with Shift

Certain control applications require that several Booleans be packed into a single register. These packed bits can

be used as an index into a table of constants or a jump table, which permits complex Boolean functions and/or

state machines to be evaluated efficiently.

To facilitate the packing of Boolean results into a register, compound Compare with Shift instructions (for example

SH.EQ) are supported.

The result of the comparison is placed in the least-significant bit of the result after the contents of the destination

register have been shifted left by one position.

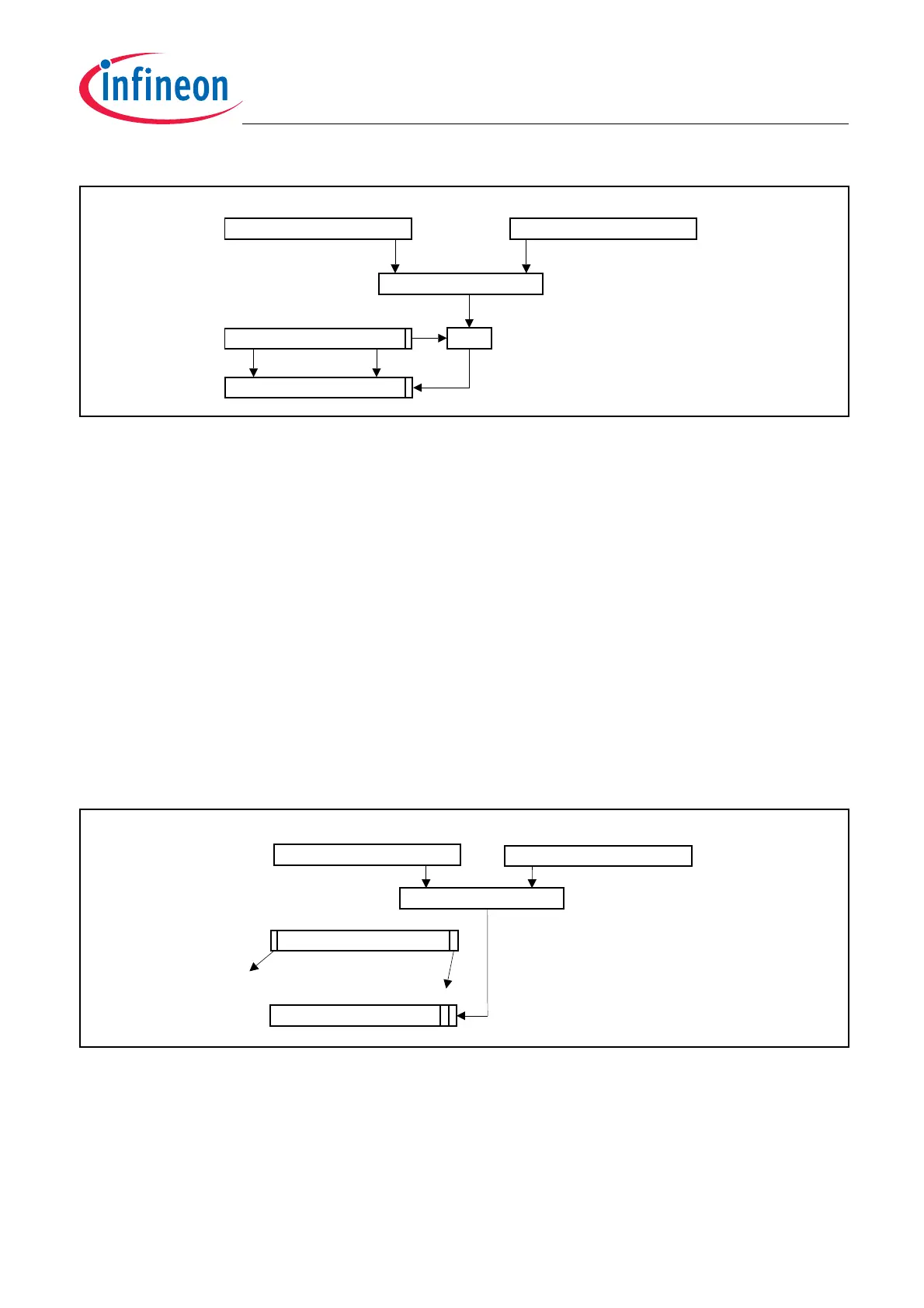

Figure 2-10 illustrates the operation of the SH.LT (Shift Less Than) instruction.

Figure 2-10 SH.LT Instruction

2.5.4 Packed Compare

For packed bytes, there are special compare instructions that perform four individual byte comparisons and

produce a 32-bit mask consisting of four ‘extended’ Booleans.

For example, EQ.B yields a result where individual bytes are FF

H

for a match, or 00

H

for no match. Similarly for

packed half-words there are special compare instructions that perform two individual half-word comparisons and

TC1052B

A

D[a]

D[b]

B

31 0 31 0

D[c]

031

D[c]

031

op

op = AND, OR or XOR

A < B ?

Discarded

TC1053B

A

D[a]

D[b]

B

31 0

31 0

D[c]

0

31

D[c]

031

Left shift 1

A < B ?

1

2

Loading...

Loading...