TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set Overview

V1.0 2013-07

User Manual (Volume 2) 2-23

2.12.3 Access to the Core Special Function Registers (CSFRs)

The core accesses the CSFRs through two instructions:

•MFCR

– The Move From Core Register instruction moves the contents of the addressed CSFR into a data register.

MFCR can be executed in any mode (i.e. User-1, User-0 or Supervisor mode).

•MTCR

– The Move To Core Register instruction moves the contents of a data register to the addressed CSFR. To

prevent unauthorized writes to the CSFRs the MTCR instruction can only be executed in Supervisor mode.

An MTCR instruction should be followed by an ISYNC instruction. This ensures that all instructions following

the MTCR see the effects of the CSFR update.

There are no instructions allowing bit, bit-field or load-modify-store accesses to the CSFRs. The RSTV instruction

(Reset Overflow Flags) only resets the overflow flags in the PSW without modifying any of the other PSW bits.

This instruction can be executed in any mode (i.e. User-1, User-0 or Supervisor mode).

The CSFRs are also mapped into the memory address space. This mapping makes the complete architectural

state of the core visible in the address map, which allows efficient debug and emulator support. Note that it is not

permitted for the core to access the CSFRs through this mechanism. The core must use MFCR and MTCR.

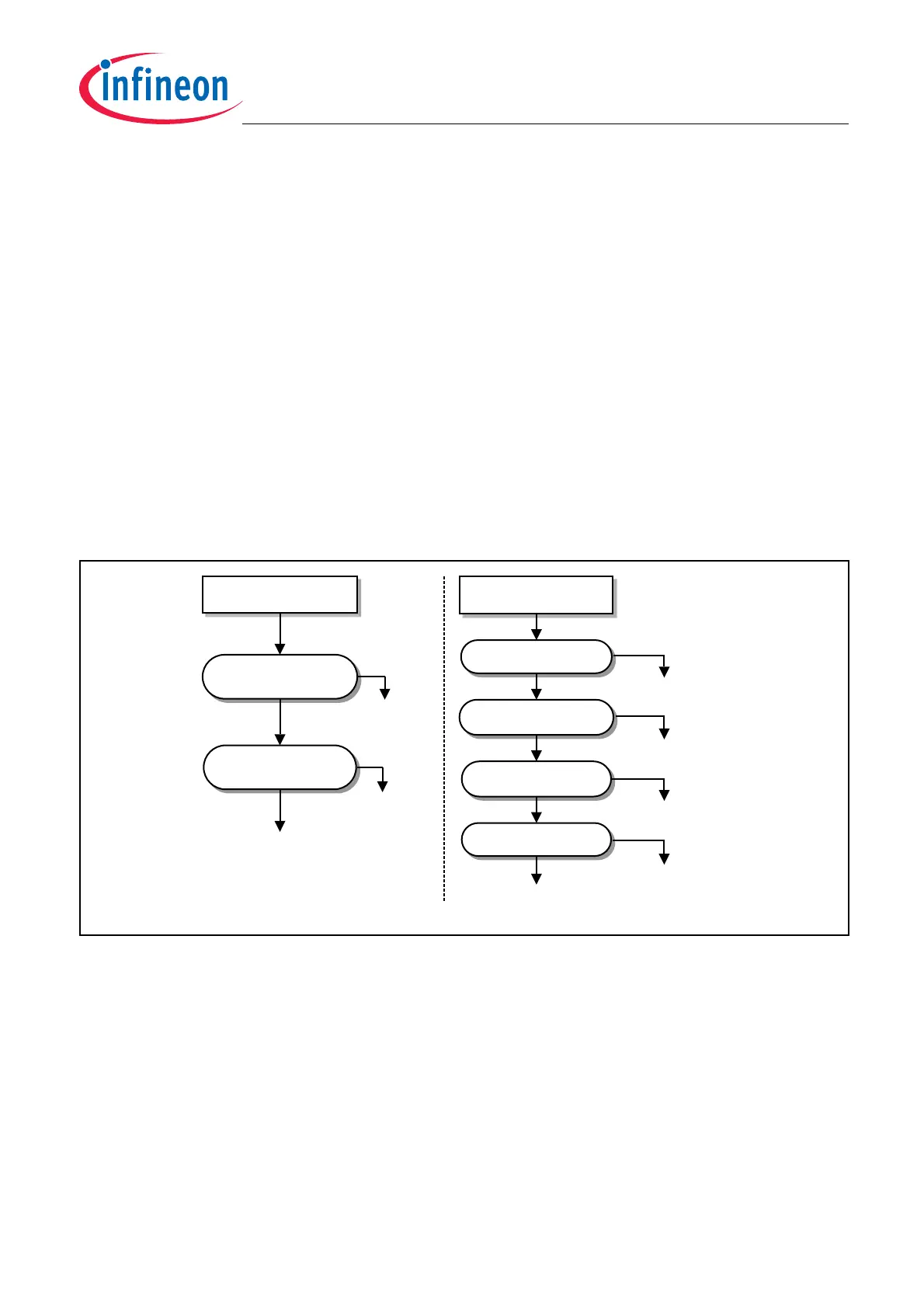

Figure 2-18 summarizes TriCore core behaviour when accessing CSFRs.

Figure 2-18 TriCore, Core Behaviour Accessing CSFRs

2.12.4 Enabling and Disabling the Interrupt System

For non-interruptible operations, the ENABLE and DISABLE instructions allow the explicit enabling and disabling

of interrupts in both User and Supervisor mode. While disabled, an interrupt will not be taken by the CPU

regardless of the relative priorities of the CPU and the highest interrupt pending. The only ‘interrupt’ that is serviced

while interrupts are disabled is the NMI (Non-Maskable Interrupt), because it bypasses the normal interrupt

structure.

If a user process accidentally disables interrupts for longer than a specified time, watchdog timers can be used to

recover.

TC1062B

Read CSFR

MFCR Da, CSFR_addr

Is CSFR_addr Word

aligned ?

Unimplemented

Register ?

Write CSFR

MFCR CSFR_addr, Da

Supervisor Mode ?

Is CSFR_addr Word

aligned ?

Is register read-only ?

Unimplemented

Register ?

No

No

Yes

Yes

Return

undefined value

Da = CSFR

Privilege trap

No effect

No effect

No effect

No

CSFR = Da

No

Yes

Yes

No

No

Yes

Yes

Return

undefined value

Loading...

Loading...