TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-177

LT

Less Than

LT.U

Less Than Unsigned

Description

If the contents of data register D[a] are less than the contents of either data register D[b] (instruction format RR)

or const9 (instruction format RC), then set the least-significant bit of D[c] to one and clear the remaining bits to

zero; otherwise clear all bits in D[c].

The operands are treated as signed (LT) or unsigned (LT.U) integers. The const9 value is sign-extended (LT) or

zero-extended (LT.U).

LTD[c], D[a], const9 (RC)

result = (D[a] < sign_ext(const9));

D[c] = zero_ext(result);

LTD[c], D[a], D[b] (RR)

result = (D[a] < D[b]);

D[c] = zero_ext(result);

LTD[15], D[a], const4 (SRC)

LTD[15], D[a], D[b] (SRR)

If the contents of data register D[a] are less than the contents of either data register D[b] (instruction format SRR)

or const4 (instruction format SRC), set the least-significant bit of D[15] to one and clear the remaining bits to zero;

otherwise clear all bits in D[15]. The operands are treated as signed 32-bit integers, and the const4 value is sign-

extended.

result = (D[a] < sign_ext(const4));

D[15] = zero_ext(result);

result = (D[a] < D[b]);

D[15] = zero_ext(result);

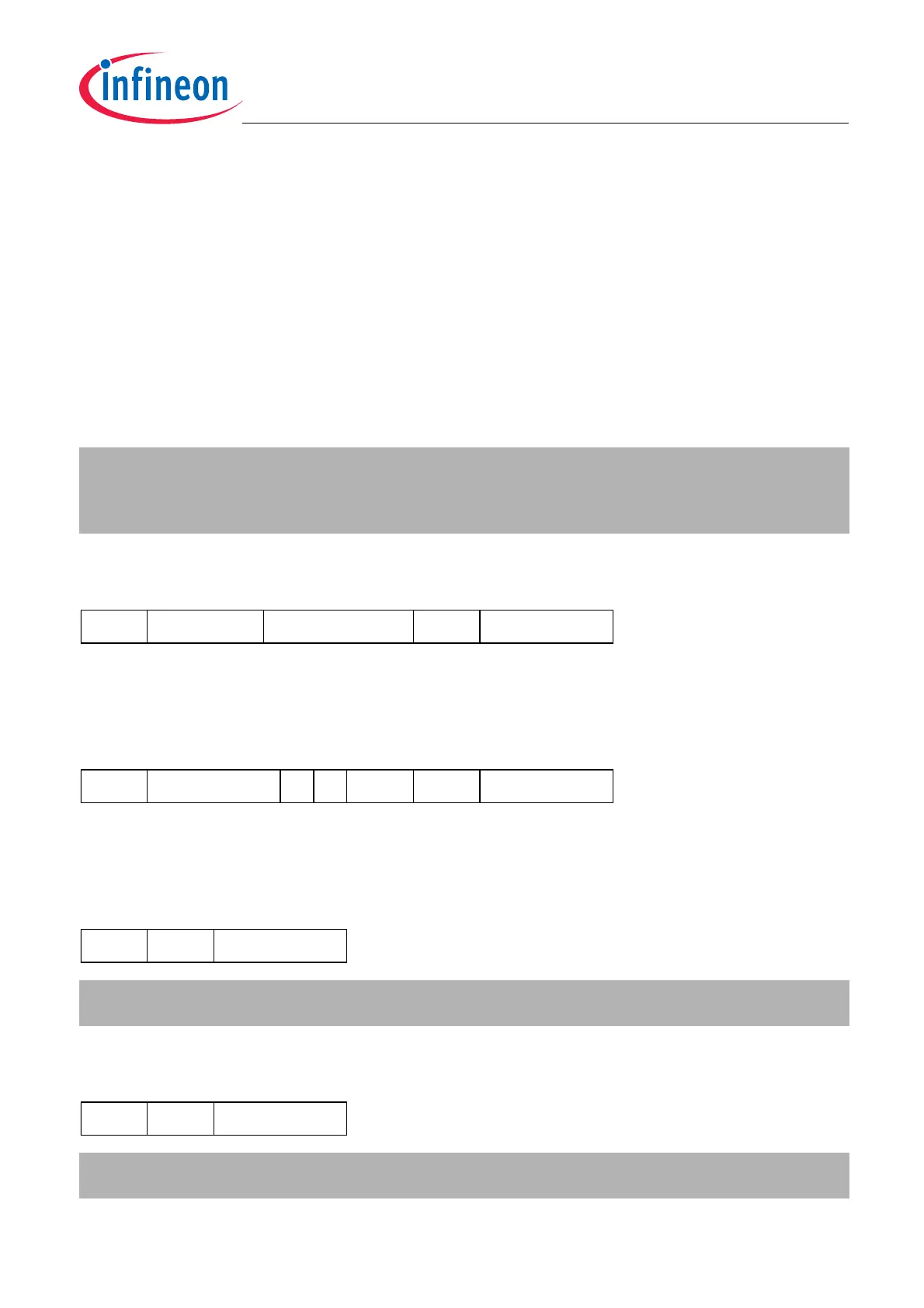

31

c

28 27

12

H

21 20

const9

12 11

a

8 7

8B

H

0

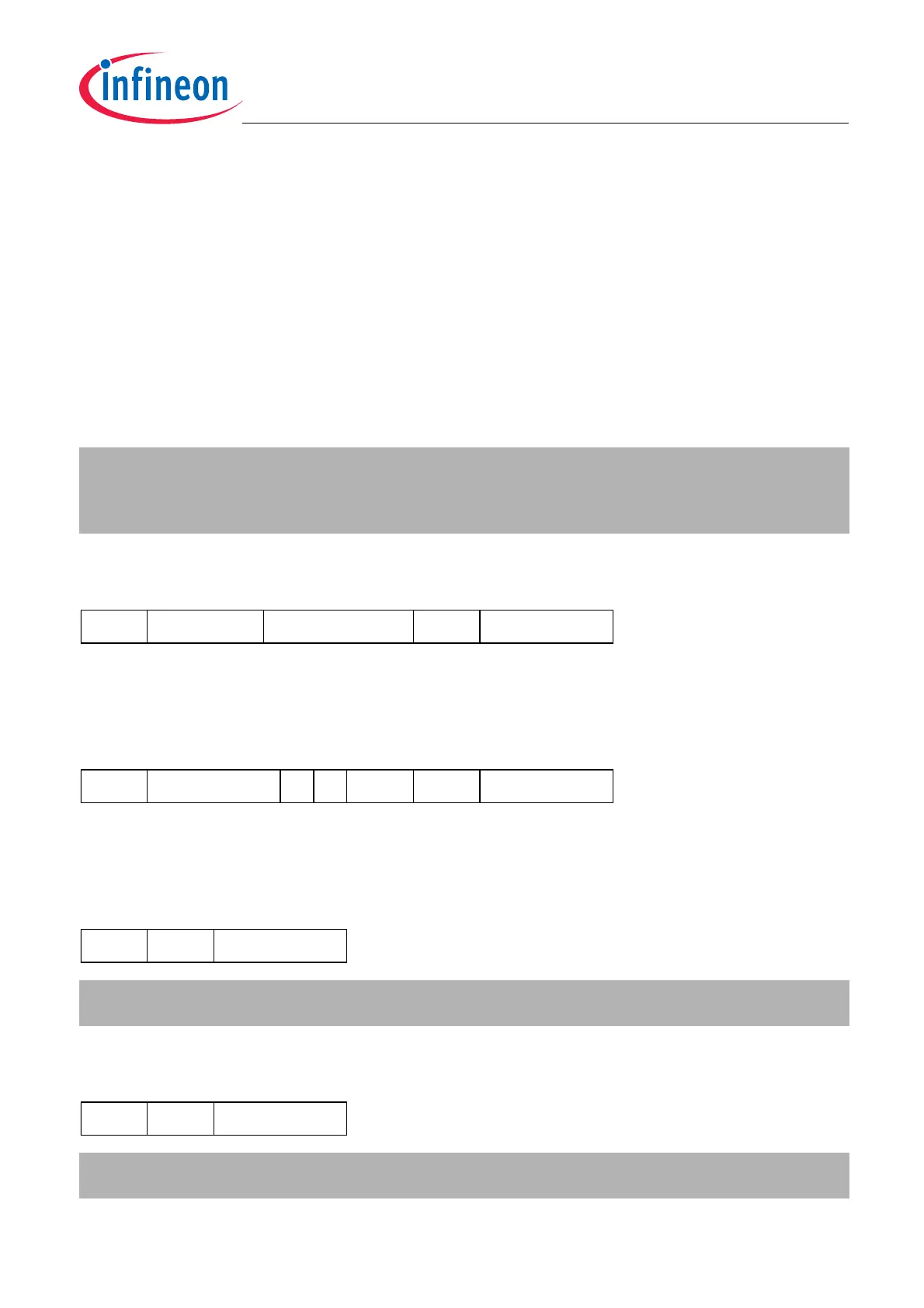

31

c

28 27

12

H

20 19

-

18 17

-

16 15

b

12 11

a

8 7

0B

H

0

Loading...

Loading...