TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-27

ADDSC.A

Add Scaled Index to Address

ADDSC.AT

Add Bit-Scaled Index to Address

Description

For ADDSC.A, left-shift the contents of data register D[a] by the amount specified by n, where n can be 0, 1, 2, or

3. Add that value to the contents of address register A[b] and put the result in address register A[c].

For ADDSC.AT, right-shift the contents of D[a] by three (with sign fill). Add that value to the contents of address

register A[b] and clear the bottom two bits to zero. Put the result in A[c]. The ADDSC.AT instruction generates the

address of the word containing the bit indexed by D[a], starting from the base address in A[b].

ADDSC.AA[c], A[b], D[a], n (RR)

A[c] = A[b] + (D[a] << n);

ADDSC.AA[a], A[b], D[15], n (SRRS)

ADDSC.ATA[c], A[b], D[a] (RR)

A[c] = (A[b] + (D[a] >> 3)) & 32’hFFFFFFFC;

Status Flags

Examples

addsc.a a3, a4, d2, #2

addsc.at a3, a4, d2

Left-shift the contents of data register D[15] by the amount specified by n, where n can be 0, 1, 2, or 3. Add that

value to the contents of address register A[b] and put the result in address register A[a].

A[a] = (A[b] + (D[15] << n));

C Not set by these instructions.

V Not set by these instructions.

SV Not set by these instructions.

AV Not set by these instructions.

SAV Not set by these instructions.

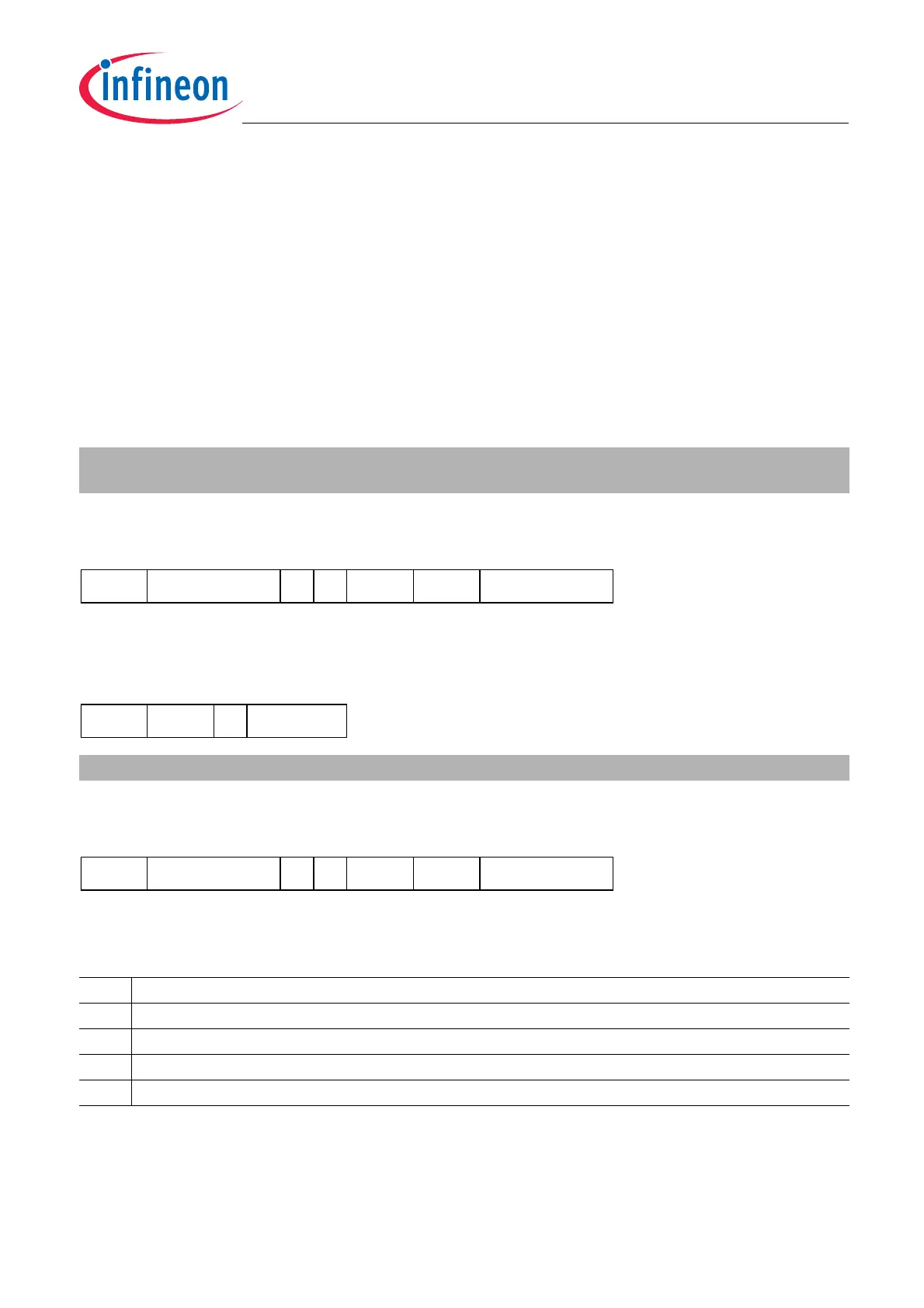

31

c

28 27

60

H

20 19

-

18 17

n

16 15

b

12 11

a

8 7

01

H

0

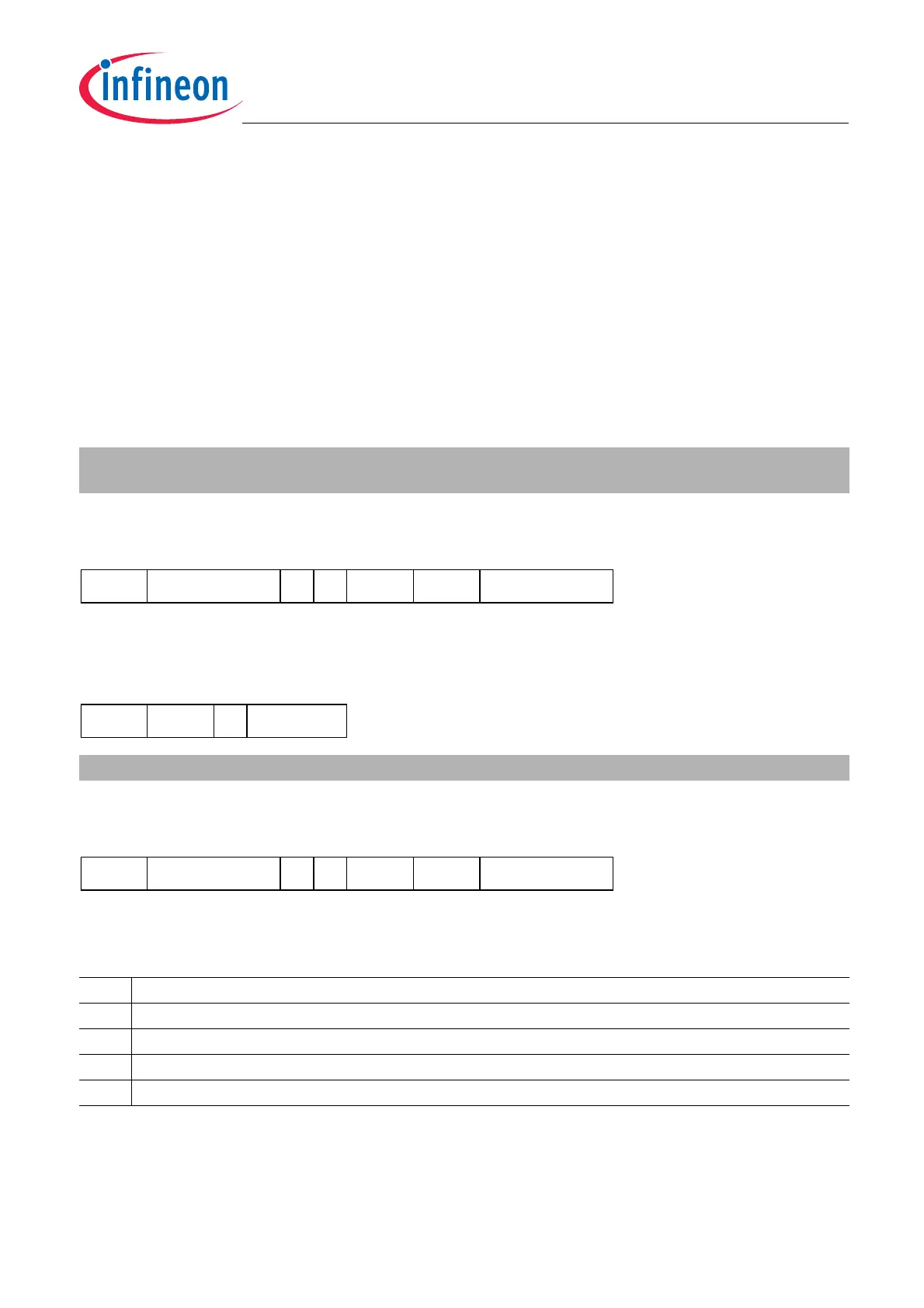

31

c

28 27

62

H

20 19

-

18 17

-

16 15

b

12 11

a

8 7

01

H

0

Loading...

Loading...