TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-115

INSERT

Insert Bit Field

Description

Starting at bit zero, extract from either D[b] (instruction formats RRRR, RRRW, RRPW) or const4 (instruction

formats RCRR, RCRW, RCPW) the number of consecutive bits specified by either E[d][36:32] (formats RRRR,

RCRR) or width (formats RRRW, RRPW, RCRW, RCPW).

Shift the result left by the number of bits specified by either E[d][4:0] (formats RRRR, RCRR), D[d] (formats RRRW,

RCRW) or pos (formats RRPW, RCPW); extract a copy of D[a], clearing the bits starting at the bit position specified

by either E[d][4:0] (formats RRRR, RCRR), D[d] (formats RRRW, RCRW) or pos (formats RRPW, RCPW), and

extending for the number of bits specified by either E[d][36:32] (formats RRRR, RCRR) or width (formats RRRW,

RRPW, RCRW, RCPW). Put the bitwise OR of the two extracted words into D[c].

INSERTD[c], D[a], const4, pos, width (RCPW)

mask = (2

width

-1) << pos;

D[c] = (D[a] & ~mask) | ((zero_ext(const4) << pos) & mask);

If pos + width > 32, then the result is undefined.

INSERTD[c], D[a], const4, E[d] (RCRR)

width = E[d][36:32];

mask = (2

width

-1) << E[d][4:0];

D[c] = (D[a] & ~mask) | ((zero_ext(const4) << E[d][4:0]) & mask);

If E[d][4:0] + E[d][36:32] > 32, then the result is undefined.

INSERTD[c], D[a], const4, D[d], width (RCRW)

mask = (2

width

-1) << D[d][4:0];

D[c] = (D[a] & ~mask) | ((zero_ext(const4) << D[d][4:0]) & mask);

If D[d][4:0] + width > 32, then the result is undefined.

INSERTD[c], D[a], D[b], pos, width (RRPW)

mask = (2

width

-1) << pos;

D[c] = (D[a] & ~mask) | ((D[b] << pos) & mask);

If pos + width > 32, then the result is undefined.

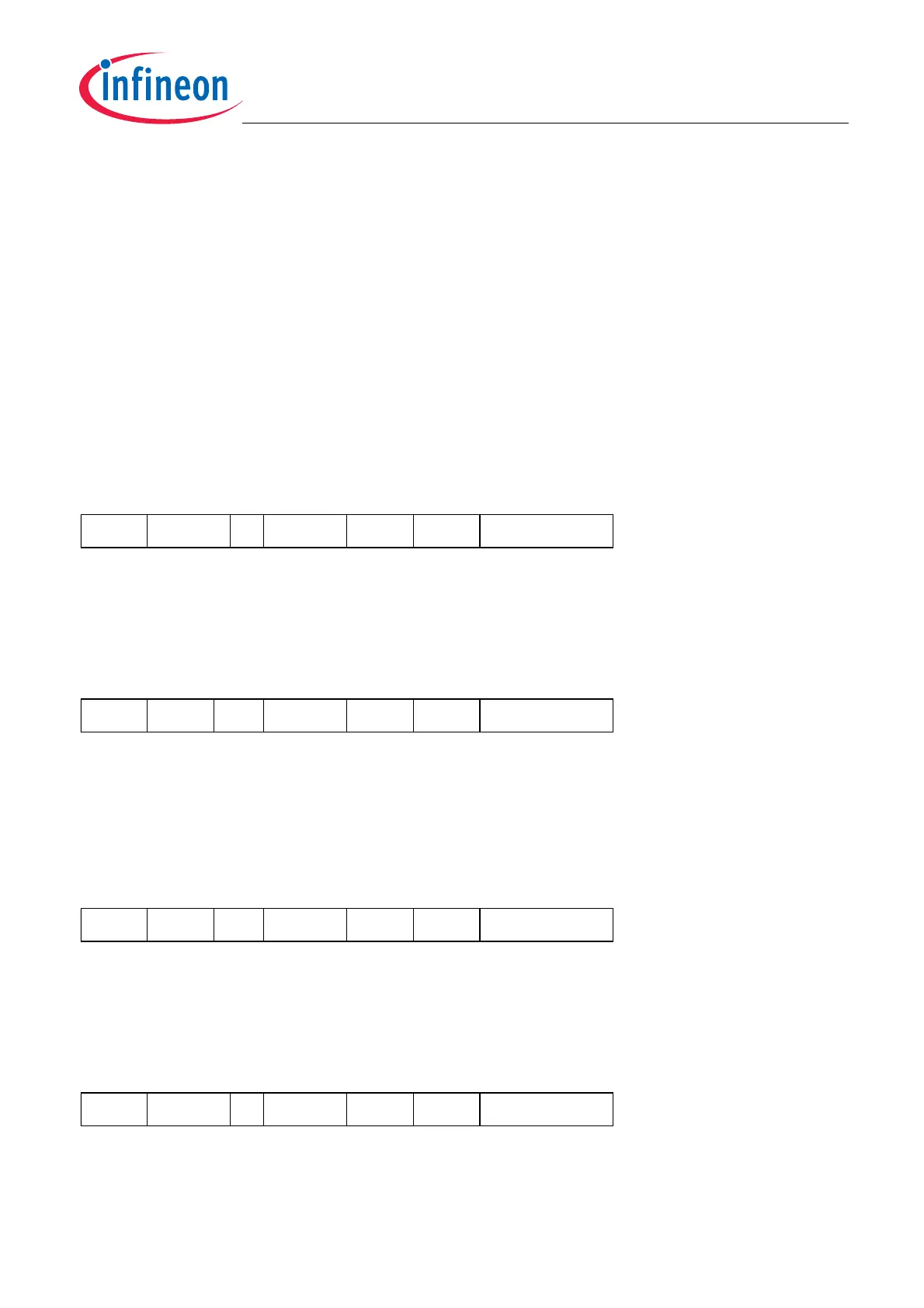

31

c

28 27

pos

23 22

00

H

21 20

width

16 15

const4

12 11

a

8 7

B7

H

0

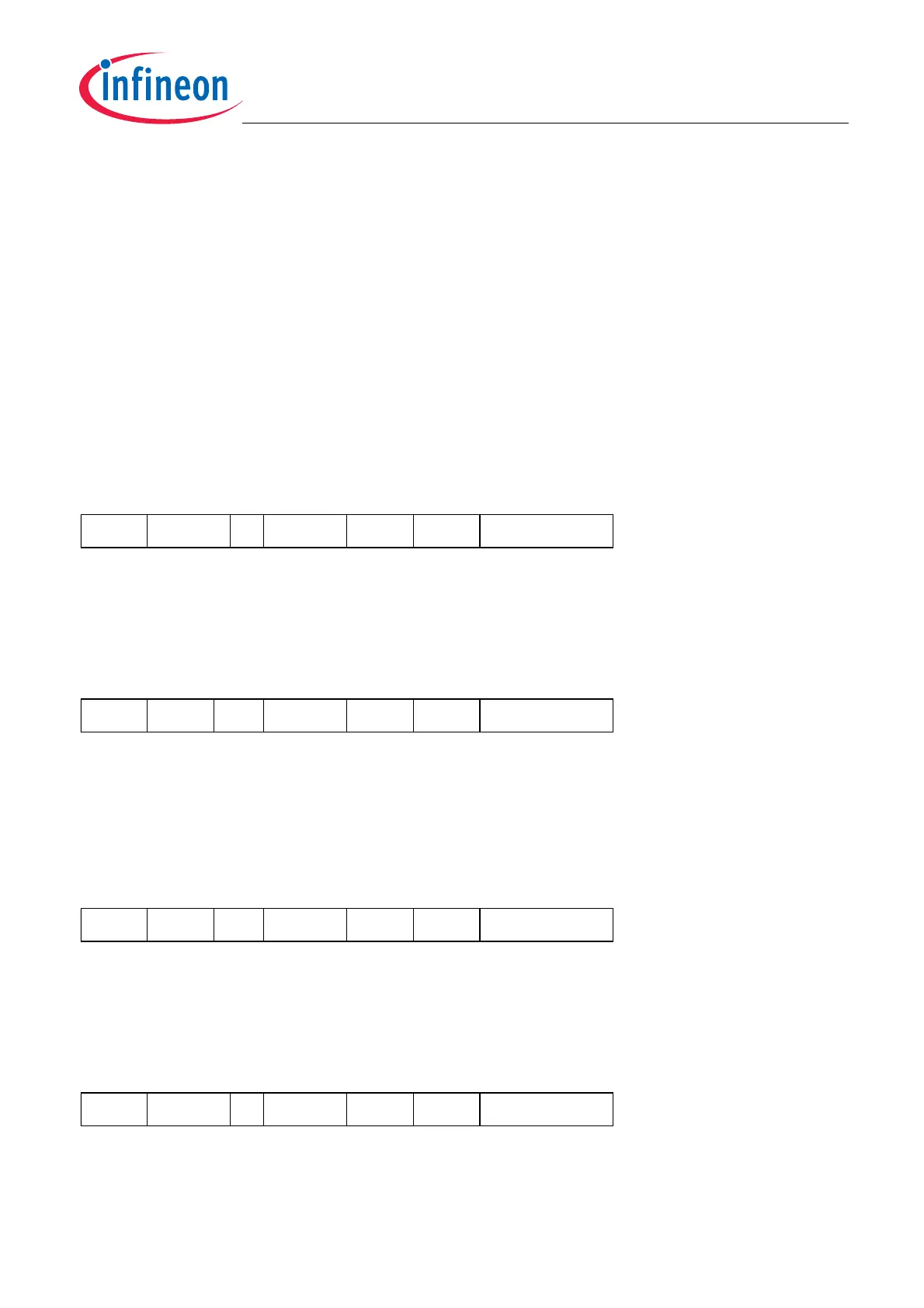

31

c

28 27

d

24 23

00

H

21 20

-

16 15

const4

12 11

a

8 7

97

H

0

31

c

28 27

d

24 23

00

H

21 20

width

16 15

const4

12 11

a

8 7

D7

H

0

31

c

28 27

pos

23 22

00

H

21 20

width

16 15

b

12 11

a

8 7

37

H

0

Loading...

Loading...