TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-366

STUCX

Store Upper Context

Description

Store the contents of registers A[10] to A[15], D[8] to D[15], and the current PSW (the registers which comprise a

task’s upper context) to the memory block specified by the addressing mode. For this instruction, the addressing

mode is limited to absolute (ABS) or base plus short offset (BO).

Note:The effective address (EA) specified by the addressing mode must be aligned on a 16-word boundary.

Note:This instruction may not be used to access peripheral space.

STUCXoff18 (ABS)(Absolute Addressing Mode)

EA = {off18[17:14], 14b'0, off18[13:0]};

M(EA,16-word) = {PCXI, PSW, A[10:11], D[8:11], A[12:15], D[12:15]};

STUCXA[b], off10 (BO)(Base + Short Index Addressing Mode)

EA = A[b] + sign_ext(off10)[9:0]};

M(EA,16-word) = {PCXI, PSW, A[10:11], D[8:11], A[12:15], D[12:15]};

Status Flags

Examples

-

See Also

LDLCX, LDUCX, RSLCX, STLCX, SVLCX, STUCX

C PSW.C is read by the instruction but not changed.

V PSW.V is read by the instruction but not changed.

SV PSW.SV is read by the instruction but not changed.

AV PSW.AV is read by the instruction but not changed.

SAV PSW.SAV is read by the instruction but not changed.

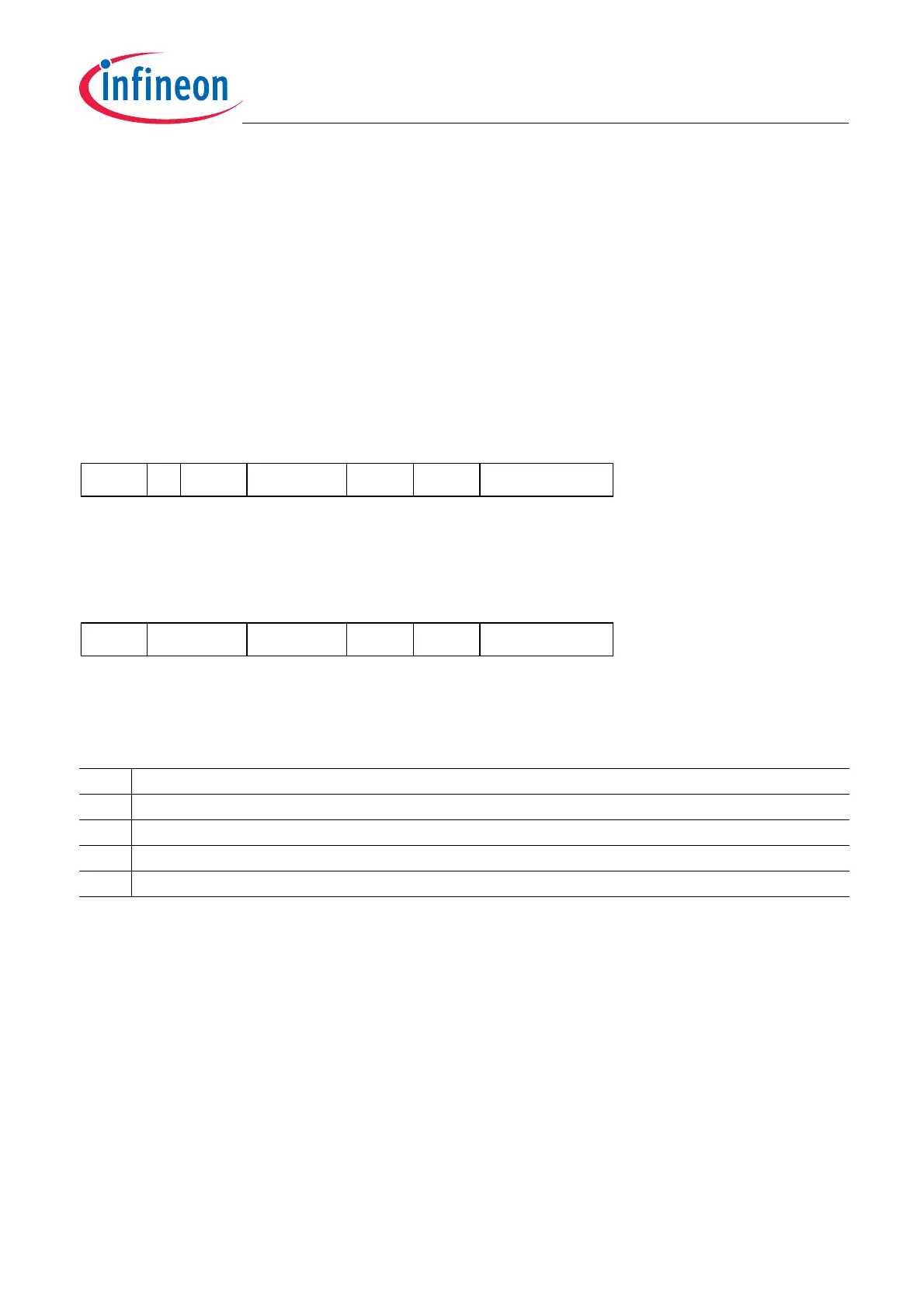

31

off18[9:6]

28 27

01

H

26 25

off18[13:10]

22 21

off18[5:0]

16 15

off18[17:14]

12 11

-

8 7

15

H

0

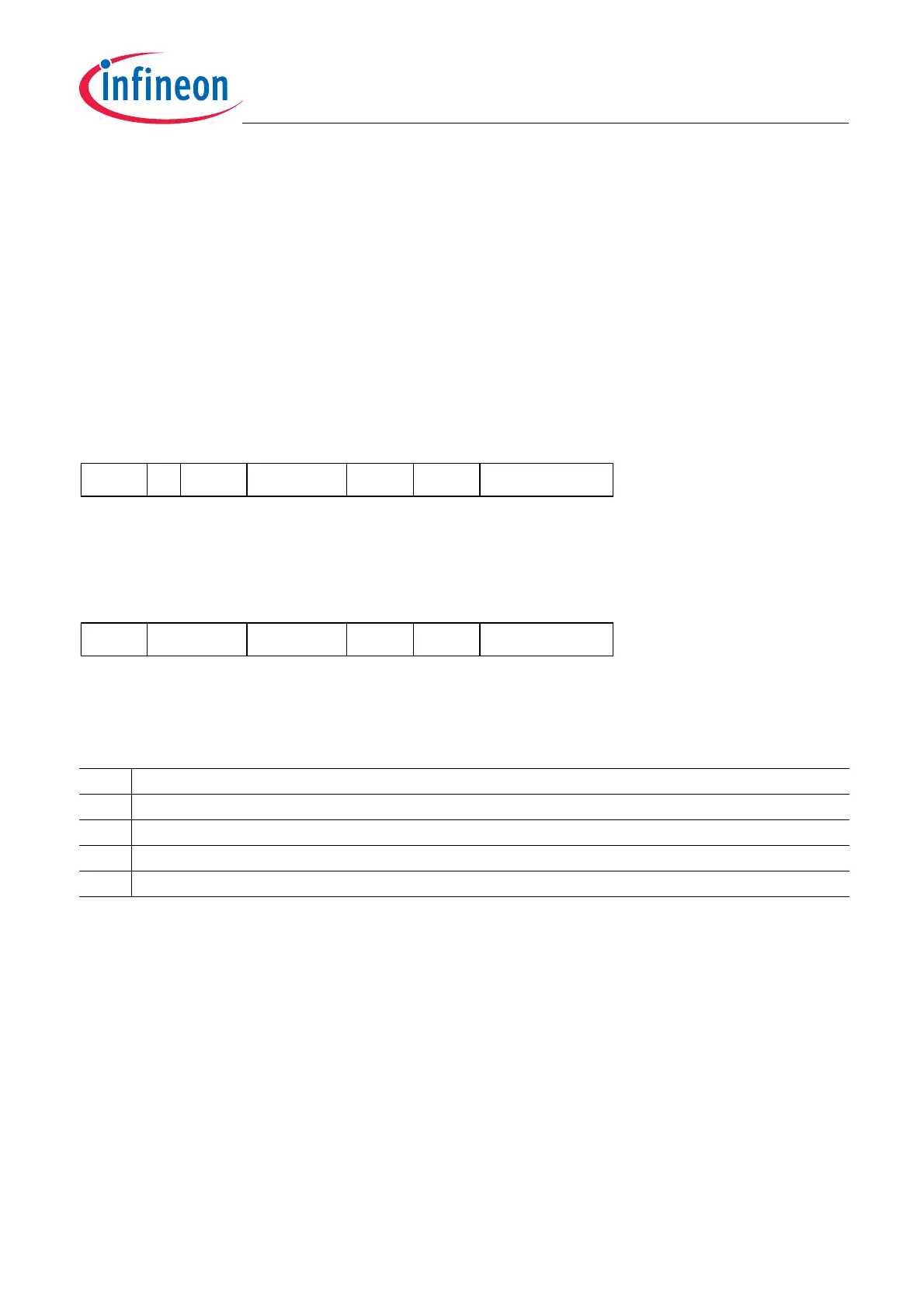

31

off10[9:6]

28 27

27

H

22 21

off10[5:0]

16 15

b

12 11

-

8 7

49

H

0

Loading...

Loading...