TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-103

EXTR

Extract Bit Field

EXTR.U

Extract Bit Field Unsigned

Description

Extract the number of consecutive bits specified by either E[d][36:32] (instruction format RRRR) or width

(instruction formats RRRW and RRPW) from D[a], starting at the bit number specified by either E[d][4:0]

(instruction format RRRR), D[d][4:0] (instruction format RRRW) or pos (instruction format RRPW). Put the result

in D[c], sign-extended (EXTR) or zero-extended (EXTR.U).

EXTRD[c], D[a], pos, width (RRPW)

D[c] = sign_ext((D[a] >> pos)[width-1:0]);

If pos + width > 32 or if width = 0, then the results are undefined.

EXTRD[c], D[a], E[d] (RRRR)

width = E[d][36:32];

D[c] = sign_ext((D[a] >> E[d][4:0])[width-1:0]);

If E[d][4:0] + width > 32 or if width = 0, then the results are undefined.

EXTRD[c], D[a], D[d], width (RRRW)

D[c] = sign_ext((D[a] >> D[d][4:0])[width-1:0]);

If D[d][4:0] + width > 32 or if width = 0, then the results are undefined.

EXTR.UD[c], D[a], pos, width (RRPW)

D[c] = zero_ext((D[a] >> pos)[width-1:0]);

If pos + width > 32 or if width = 0, then the results are undefined.

EXTR.UD[c], D[a], E[d] (RRRR)

width = E[d][36:32];

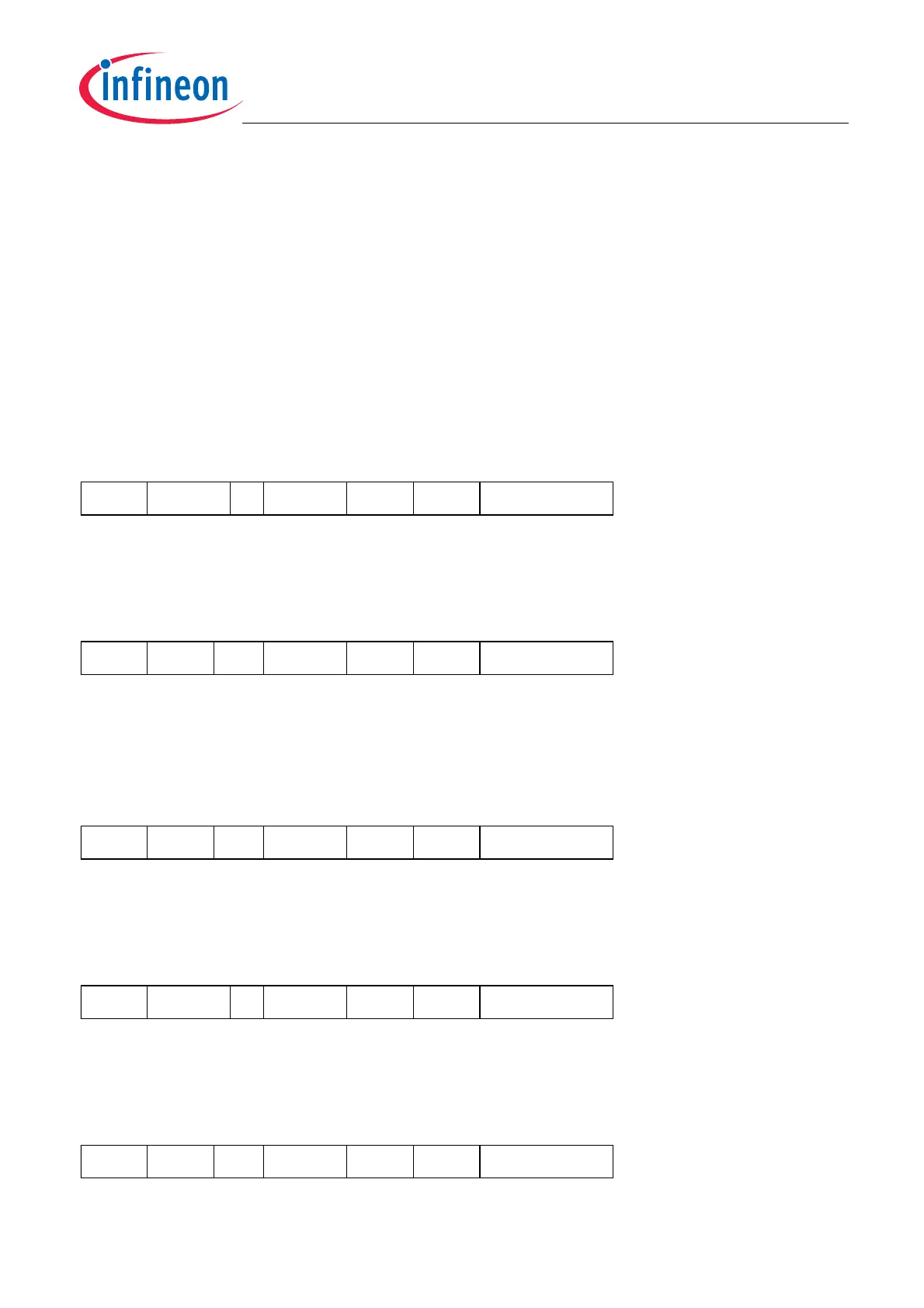

31

c

28 27

pos

23 22

02

H

21 20

width

16 15

-

12 11

a

8 7

37

H

0

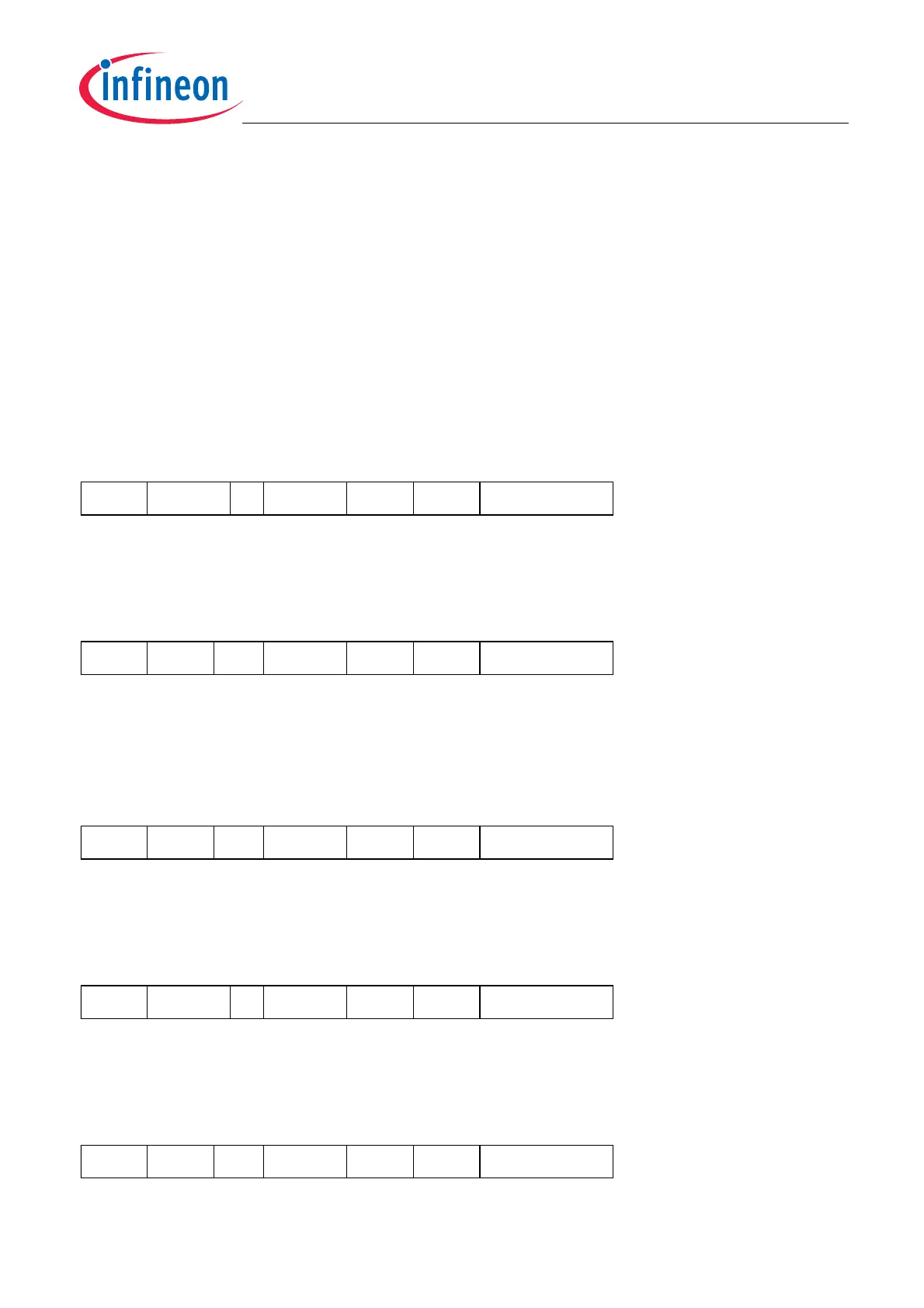

31

c

28 27

d

24 23

02

H

21 20

-

16 15

-

12 11

a

8 7

17

H

0

31

c

28 27

d

24 23

02

H

21 20

width

16 15

-

12 11

a

8 7

57

H

0

31

c

28 27

pos

23 22

03

H

21 20

width

16 15

-

12 11

a

8 7

37

H

0

31

c

28 27

d

24 23

03

H

21 20

-

16 15

-

12 11

a

8 7

17

H

0

Loading...

Loading...