TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-344

SHAS

Arithmetic Shift with Saturation

Description

If the shift count specified through the contents of either D[b] (instruction format RR) or const9 (instruction format

RC) is greater than or equal to zero, then left-shift the value in D[a] by the amount specified by shift count. The

vacated bits are filled with zeros and the result is saturated if its sign bit differs from the sign bits that are shifted

out. If the shift count is less than zero, right-shift the value in D[a] by the absolute value of the shift count. The

vacated bits are filled with the sign-bit (the most significant bit) and bits shifted out are discarded. Put the result in

D[c]. The shift count is a 6-bit signed number, derived from D[b][5:0] (format RR) or const9[5:0] (format RC).

The range for the shift count is -32 to +31, allowing shift left up to 31 bit positions and to shift right up to 32 bit

positions. Note that a shift right by 32 bits leaves all zeros or all ones in the result, depending on the sign-bit.

SHASD[c], D[a], const9 (RC)

if (const9[5:0] >= 0) then {

result = D[a] << const9[5:0];

} else {

shift_count = 0 - const9[5:0];

msk = D[a][31] ? (((1 << shift_count) - 1) << (32 - shift_count)) : 0;

result = msk | (D[a] >> shift_count);

}

D[c] = ssov(result,32);

SHASD[c], D[a], D[b] (RR)

if (D[b][5:0] >= 0) then {

result = D[a] << D[b][5:0];

} else {

shift_count = 0 - D[b][5:0];

msk = D[a][31] ? (((1 << shift_count) - 1) << (32 - shift_count)) : 0;

result = msk | (D[a] >> shift_count);

}

D[c] = ssov(result,32);

Status Flags

C Not set by this instruction.

V overflow = (result > 7FFFFFFF

H

) OR (result < -80000000

H

);

if (overflow) then PSW.V = 1 else PSW.V = 0;

SV if (overflow) then PSW.SV = 1 else PSW.SV = PSW.SV;

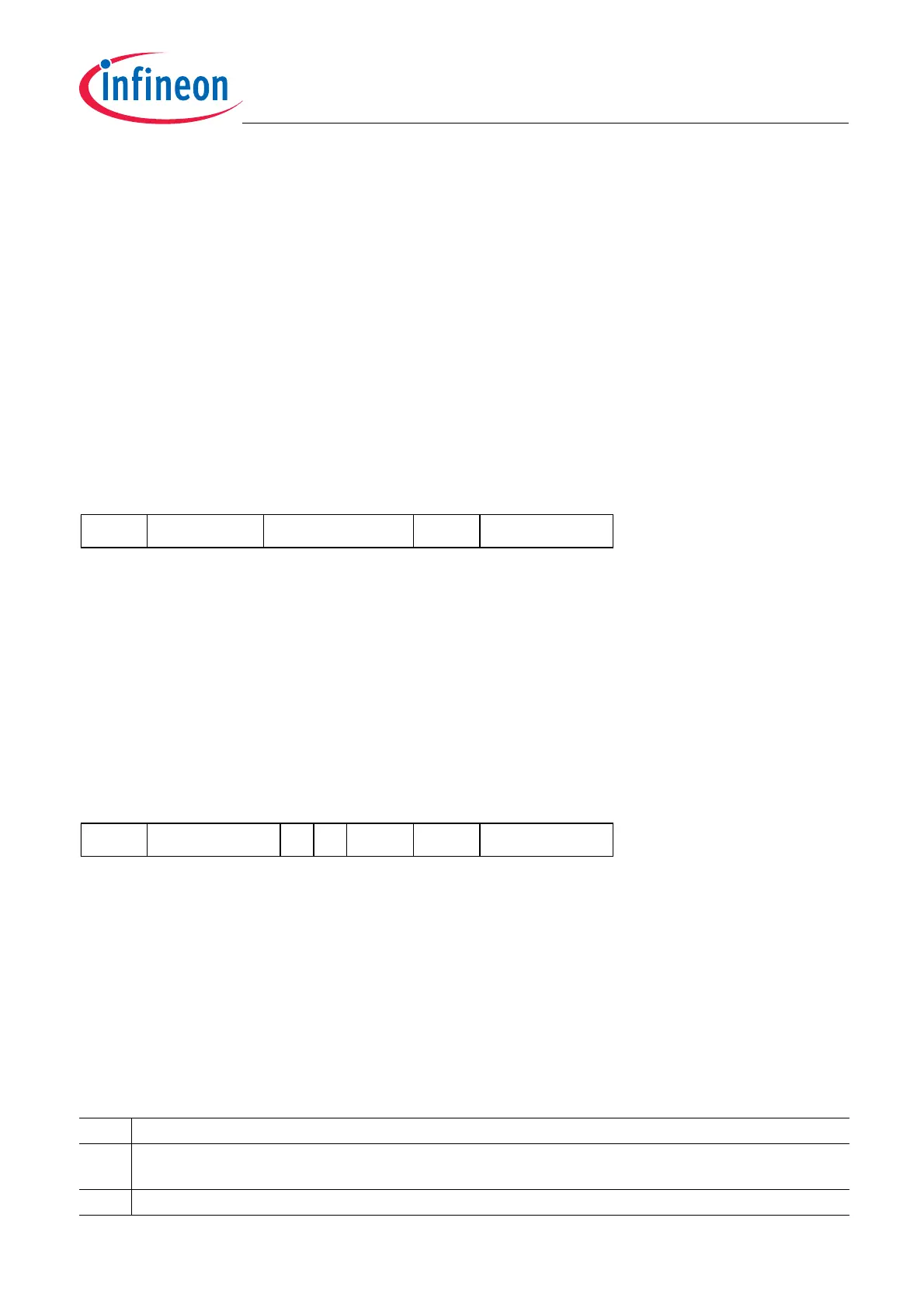

31

c

28 27

02

H

21 20

const9

12 11

a

8 7

8F

H

0

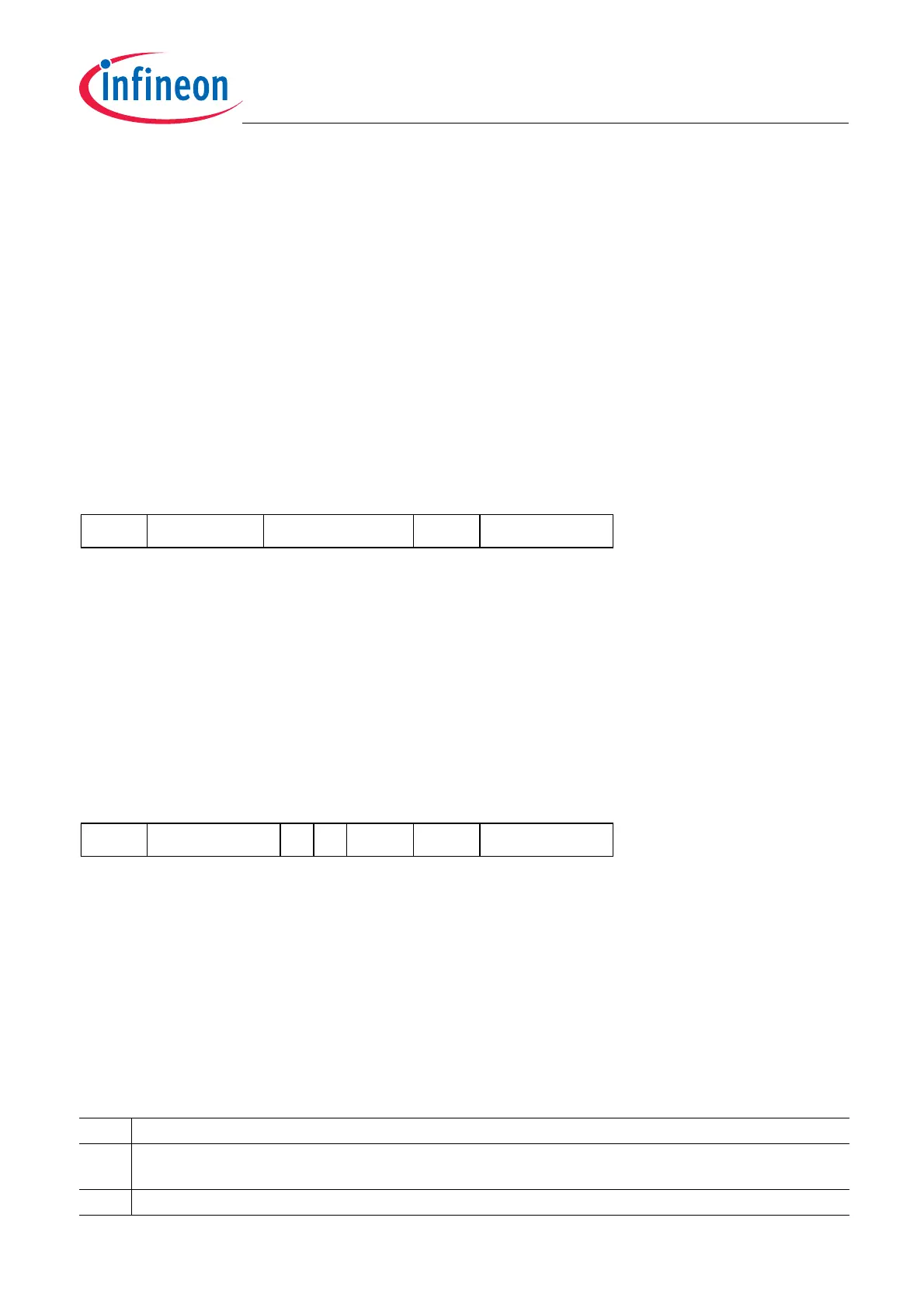

31

c

28 27

02

H

20 19

-

18 17

-

16 15

b

12 11

a

8 7

0F

H

0

Loading...

Loading...