Section 9: TSP command reference Series 2600B System SourceMeter® instrument Reference Manual

9-320 2600BS-901-01 Rev. F/August 2021

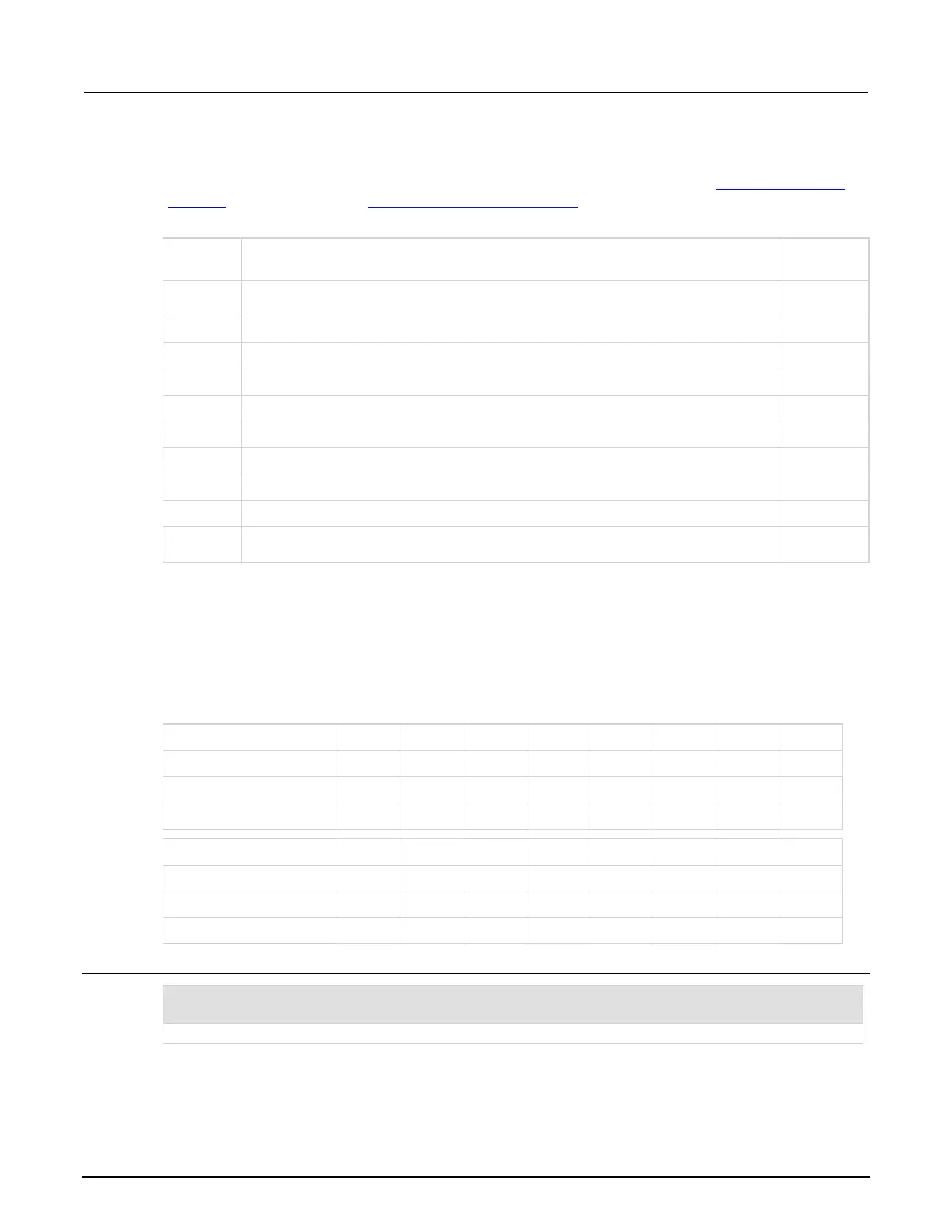

A set bit indicates the specified timer generated an action overrun because it was still processing a

delay from a previous trigger when a new trigger was received.

For information about .condition, .enable, .event, .ntr, and .ptr registers, refer to Status register set

contents (on page 12-1) and Enable and transition registers (on page 12-19). The individual bits of

this register are defined in the following table.

status.operation.instrument.trigger_timer.trigger_overrun.TMR1

status.operation.instrument.trigger_timer.trigger_overrun.TMR2

status.operation.instrument.trigger_timer.trigger_overrun.TMR3

status.operation.instrument.trigger_timer.trigger_overrun.TMR4

status.operation.instrument.trigger_timer.trigger_overrun.TMR5

status.operation.instrument.trigger_timer.trigger_overrun.TMR6

status.operation.instrument.trigger_timer.trigger_overrun.TMR7

status.operation.instrument.trigger_timer.trigger_overrun.TMR8

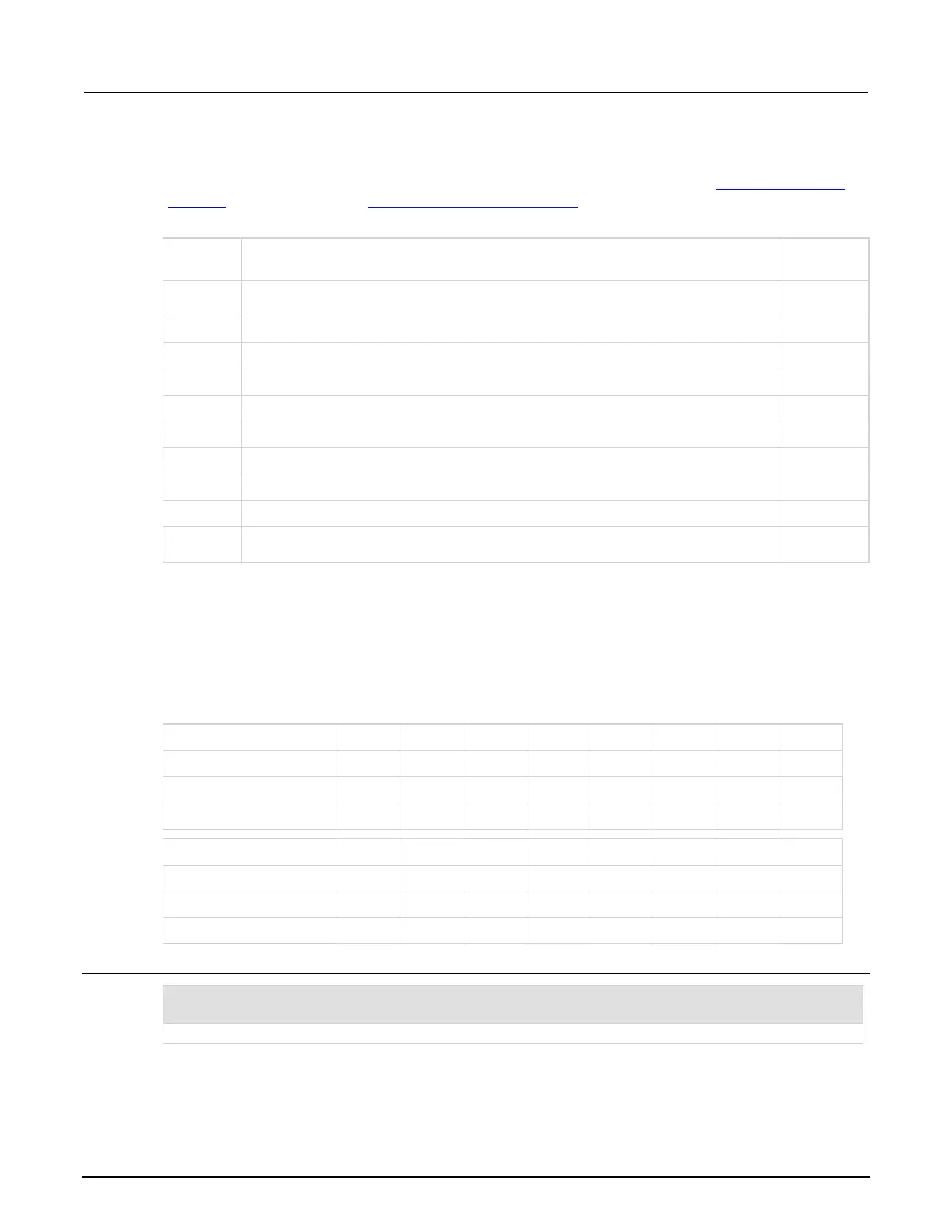

As an example, to set bit B1 of the operation status trigger timer trigger overrun enable register, set

status.operation.instrument.trigger_timer.trigger_overrun.enable =

status.operation.instrument.trigger_timer.trigger_overrun.TMR1.

In addition to the above constants, operationRegister can be set to the numeric equivalent of the

bit to set. To set more than one bit of the register, set operationRegister to the sum of their

decimal weights. For example, to set bits B1 and B4, set operationRegister to 18 (which is the

sum of 2 + 16).

status.operation.instrument.trigger_timer.trigger_overrun.enable =

status.operation.instrument.trigger_timer.trigger_overrun.TMR3

Uses a constant to set the timer 3 bit of the operation status trigger timer overrun enable register.

Loading...

Loading...