Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 160

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

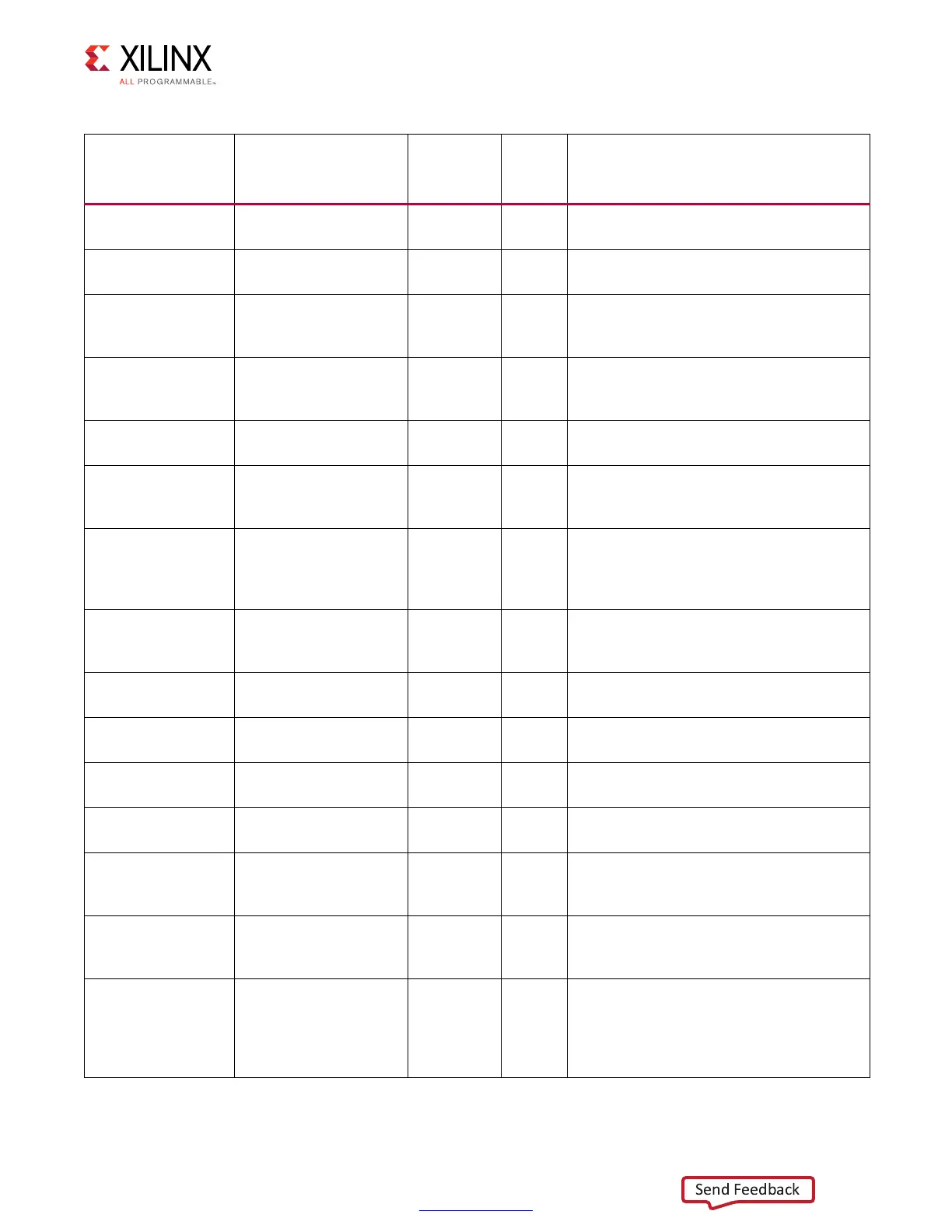

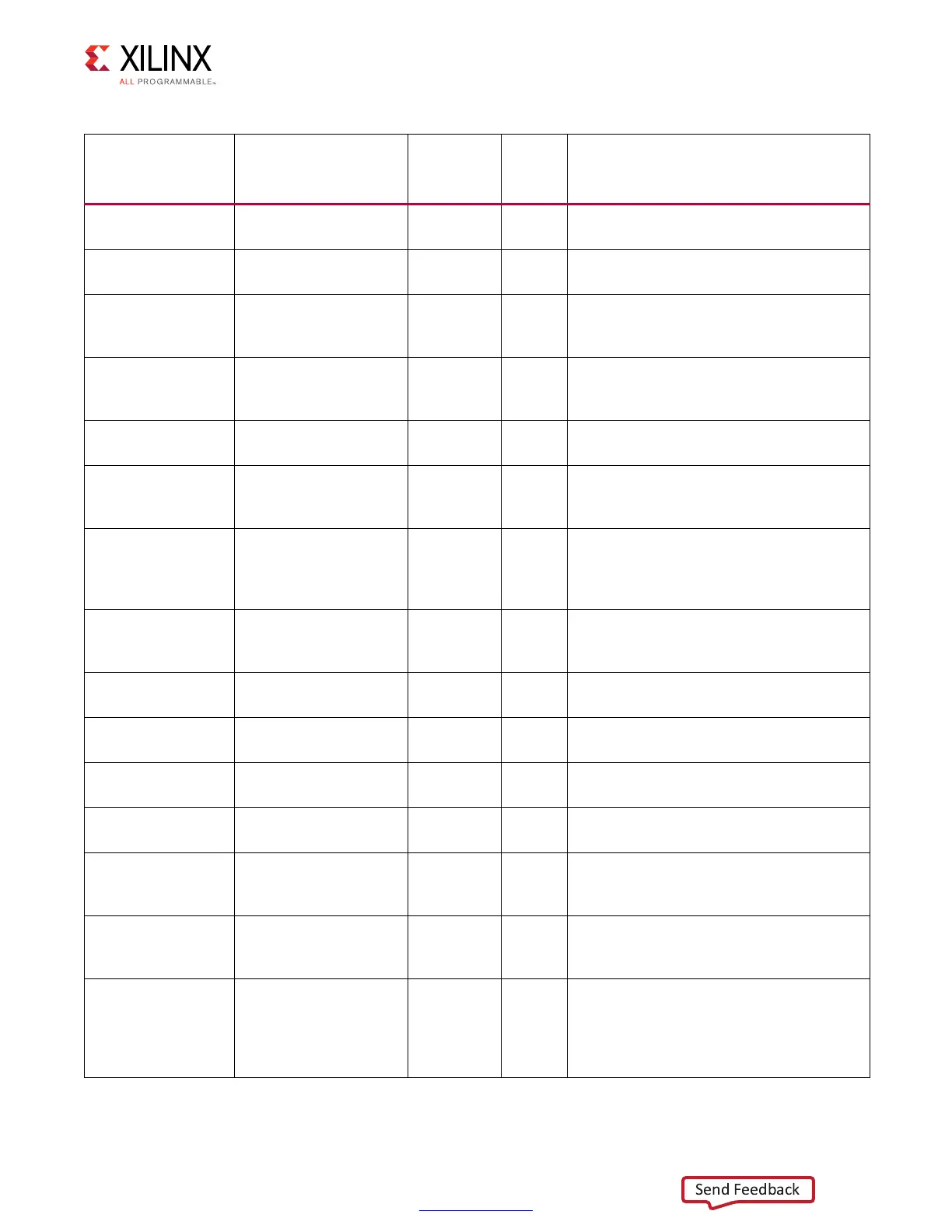

sync_pulse 1 Input –

This is the synchronization pulse output

by the PLL.

pll_lock 1 Input –

The LOCKED output of the PLL

instantiated in the infrastructure module.

mmcm_ps_clk 1 Input –

MMCM phase shifted clock used in

OCLKDELAYED calibration stage to

optimize calibration center point.

poc_sample_pd 1 Input –

Input to phase detector in OCLKDELAYED

calibration logic used for optimization of

center point.

iddr_rst 1 Input

Active-

High

Reset input to phase detector in

OCLKDELAYED calibration logic.

psen 1 Output

Active-

High

When psen is asserted for one

mmcm_ps_clk clock period, a phase shift

increment or decrement is initiated.

psincdec 1 Output

Active-

High

A High on psincdec initiates a phase

increment by 1/56th of the VCO period. A

Low on psincdec initiates a phase

decrement by 1/56th of the VCO period.

psdone 1 Input

Active-

High

The MMCM asserted this signal for one

mmcm_ps_clk period when phase shift is

completed.

mc_ras_n [nCK_PER_CLK0 – 1:0] Input

Active-

Low

mc_xxx_n[0] is the first cmd in the

sequence of four.

mc_cas_n [nCK_PER_CLK – 1:0] Input

Active-

Low

mc_xxx_n[0] is the first cmd in the

sequence of four.

mc_we_n [nCK_PER_CLK – 1:0] Input

Active-

Low

mc_xxx_n[0] is the first cmd in the

sequence of four.

mc_address

[ROW_WIDTH ×

nCK_PER_CLK – 1:0]

Input –

mc_address[ROW_WIDTH – 1:0] is the first

command address in the sequence of four.

mc_bank

[BANK_WIDTH ×

nCK_PER_CLK – 1:0]

Input –

mc_bank[BANK_WIDTH – 1:0] is the first

command bank address in the sequence

of four.

mc_cs_n

[CS_WIDTH ×

nCS_PER_RANK ×

nCK_PER_CLK – 1:0]

Input –

mc_cs_n [CS_WIDTH – 1:0] is the cs_n

associated with the first command in the

sequence.

mc_odt [1:0] Input –

mc_odt [1:0] is the ODT driven by the

controller based on the RTT_NOM and

RTT_WR values. This signal is valid when

the CKE_ODT_AUX parameter is set to

FALSE.

Table 1-61: Memory Controller to Calibration Logic Interface Signals (Cont’d)

Signal Name Width

I/O

To/From

PHY

Type Description

Loading...

Loading...