Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 235

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Determine the Failing Calibration Stage

Using the Vivado logic analyzer feature, configure the device along with debug_nets.ltx

file. This file can be found in the example.runs\impl_1\ directory after implementation

completes with Debug_port feature enabled. Observe the following debug signals in the

provided ILA core. This indicates which calibration stage failed:

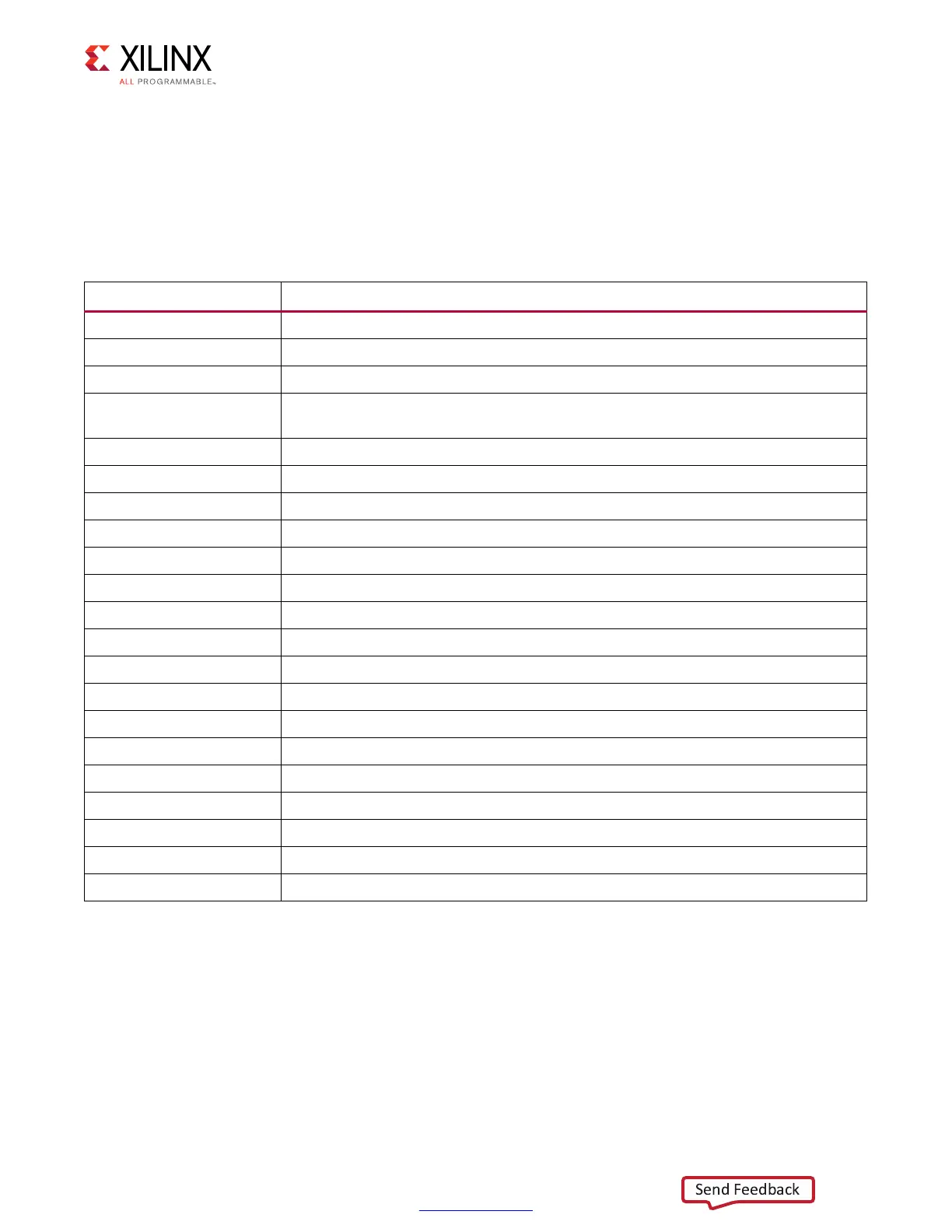

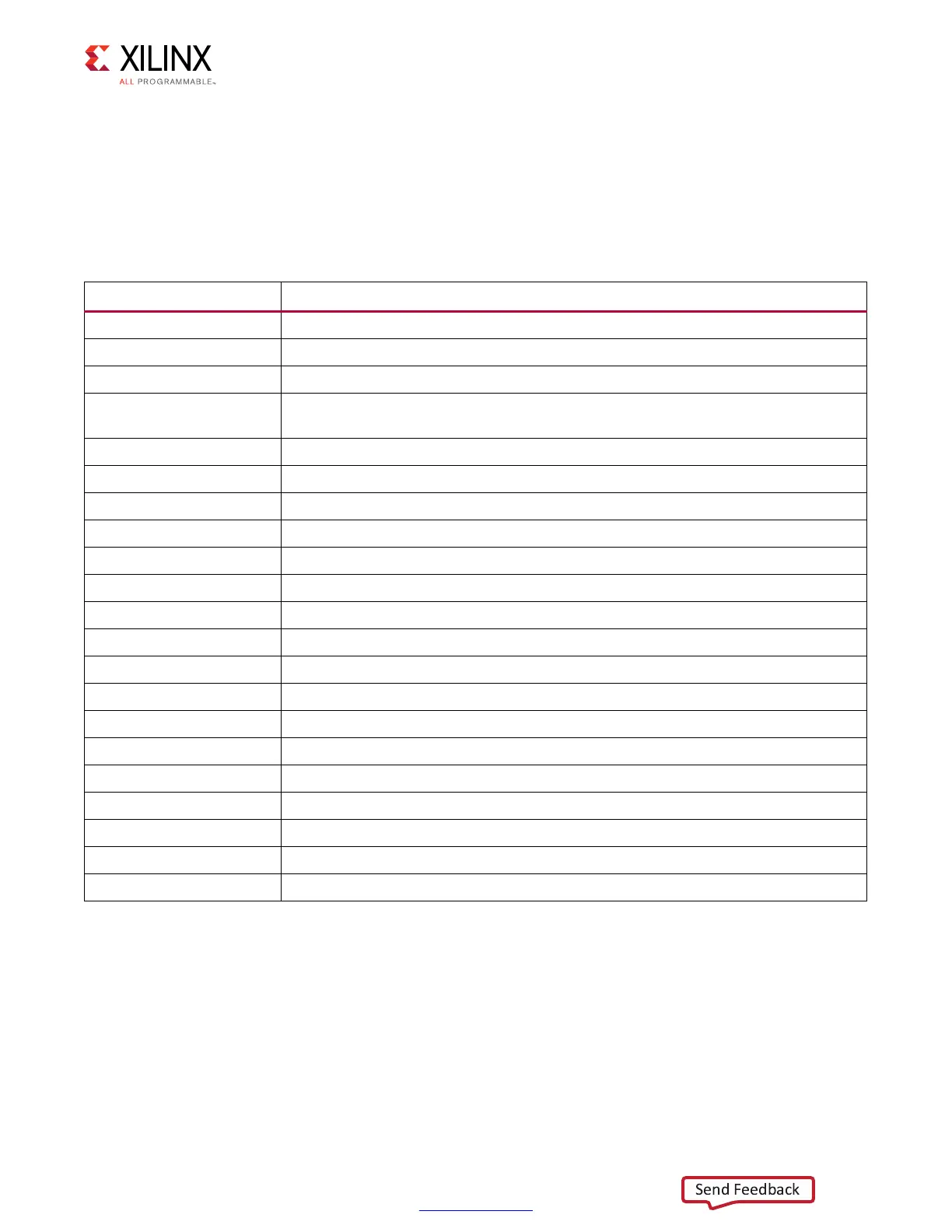

Table 1-73: DDR2/DDR3 Basic ILA Debug Signals

Signal Name Description

init_calib_complete Signifies memory initialization and calibration have completed successfully.

dbg_wrlvl_start Signifies the start of the Write Leveling stage of calibration.

dbg_wrlvl_done Signifies successful completion of the Write Leveling stage of calibration.

dbg_wrlvl_err

Signifies the Write Leveling stage of calibration exhibited errors and did not

complete.

dbg_pi_phaselock_start Signifies the start of the PHASELOCK stage of calibration.

dbg_pi_phaselock_done Signifies successful completion of the PHASELOCK stage of calibration.

dbg_pi_phaselock_err Signifies the PHASELOCK stage of calibration exhibited errors and did not complete.

dbg_pi_dqsfound_start Signifies the start of the DQSFOUND stage of calibration.

dbg_pi_dqsfound_done Signifies successful completion of the DQSFOUND stage of calibration.

dbg_pi_dqsfound_err Signifies the DQSFOUND stage of calibration exhibited errors and did not complete.

dbg_rdlvl_start[0] Signifies the start of Read Leveling Stage 1 calibration.

dbg_rdlvl_start[1] Signifies the start of the MPR stage of calibration.

dbg_rdlvl_done[0] Signifies the successful completion of Read Leveling Stage 1 calibration.

dbg_rdlvl_done[1] Signifies the successful completion of the MPR Stage of calibration.

dbg_rdlvl_err[0] Signifies Read Leveling Stage 1 calibration exhibited errors and did not complete.

dbg_rdlvl_err[1] Signifies the MPR stage of calibration exhibited errors and did not complete.

dbg_oclkdelay_calib_start Signifies the start of the OCLKDELAY stage of calibration.

dbg_oclkdelay_calib_done Signifies successful completion of the OCLKDELAY stage of calibration.

dbg_wrcal_start Signifies the start of the Write Calibration stage of calibration.

dbg_wrcal_done Signifies successful completion of the Write Calibration stage of calibration.

dbg_wrcal_err Signifies Write Calibration exhibited errors and did not complete.

Loading...

Loading...