Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 63

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

user_design/rtl/ui

This directory contains the user interface code that mediates between the native interface

of the Memory Controller and user applications (Table 1-9).

<component name>/user_design/xdc

Table 1-10 lists the modules in the user_design/xdc directory.

ddr_phy_dqs_found_cal

This module contains the Read leveling calibration logic (PHASER_IN

DQSFOUND calibration logic).

ddr_phy_init

This module contains the memory initialization and overall master

state control during initialization and calibration.

ddr_phy_rdlvl

This module contains the Read leveling Stage1 calibration logic

(Window detection with PRBS pattern).

ddr_phy_top This is the top-level module for the physical layer.

ddr_phy_wrcal This module contains the write calibration logic.

ddr_phy_wrlvl This module contains the write leveling logic.

ddr_prbs_gen

This PRBS module uses a many-to-one feedback mechanism for 2n

sequence generation.

Notes:

1. All file names are prefixed with the MIG core version number. For example, for the MIG 4.1 release module name

of ddr_byte_group_io in generated output is now mig_7series_v4_1_ddr_byte_group_io.

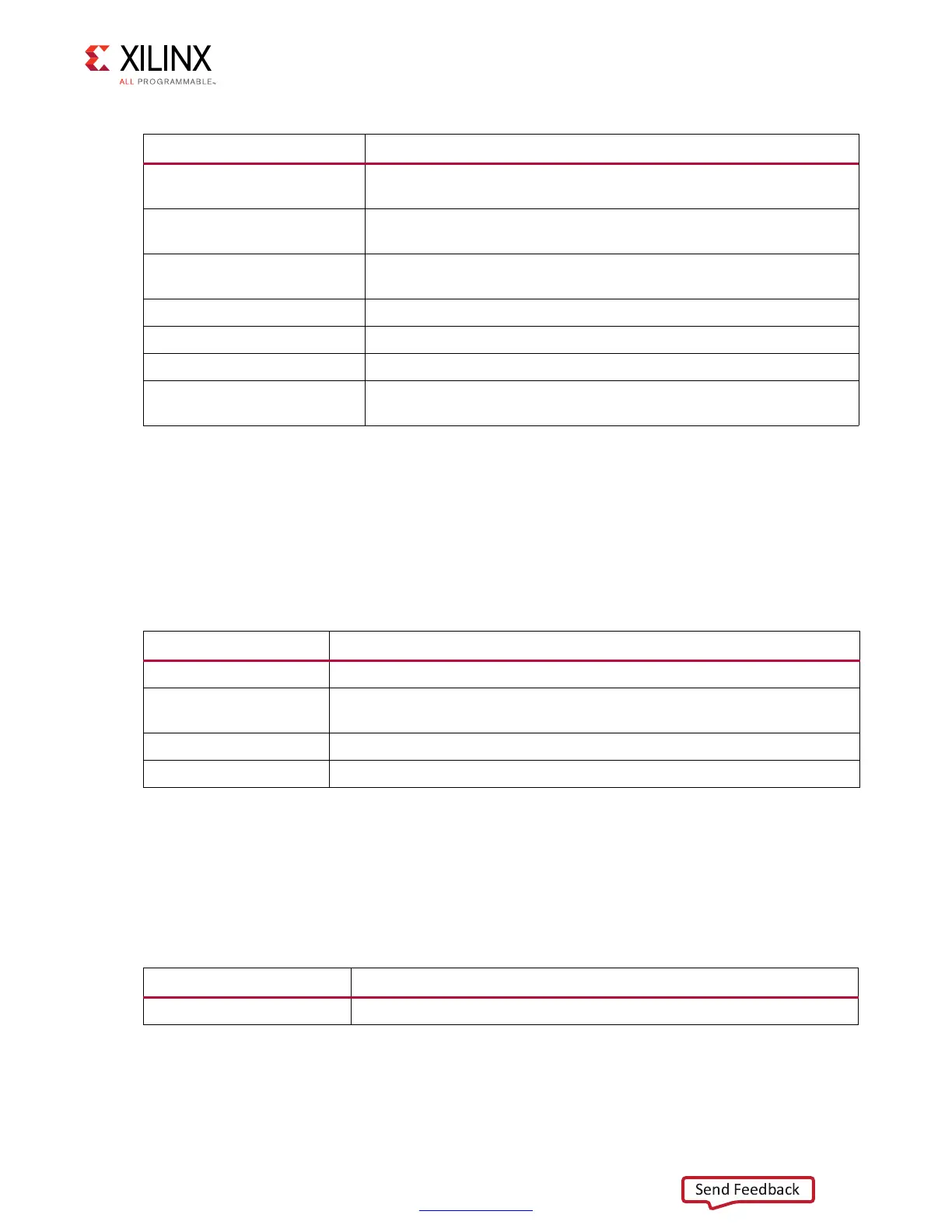

Table 1-9: Files In user_design/rtl/ui Directory

Name

(1)

Description

ui_cmd.v This is the user interface command port.

ui_rd_data.v

This is the user interface read buffer. It reorders read data returned from the

Memory Controller back to the request order.

ui_wr_data.v This is the user interface write buffer.

ui_top.v This is the top-level of the Memory Controller user interface.

Notes:

1. All file names are prefixed with the MIG core version number. For example, for the MIG 4.1 release module name

of ui_cmd in generated output is now mig_7series_v4_1_ui_cmd.

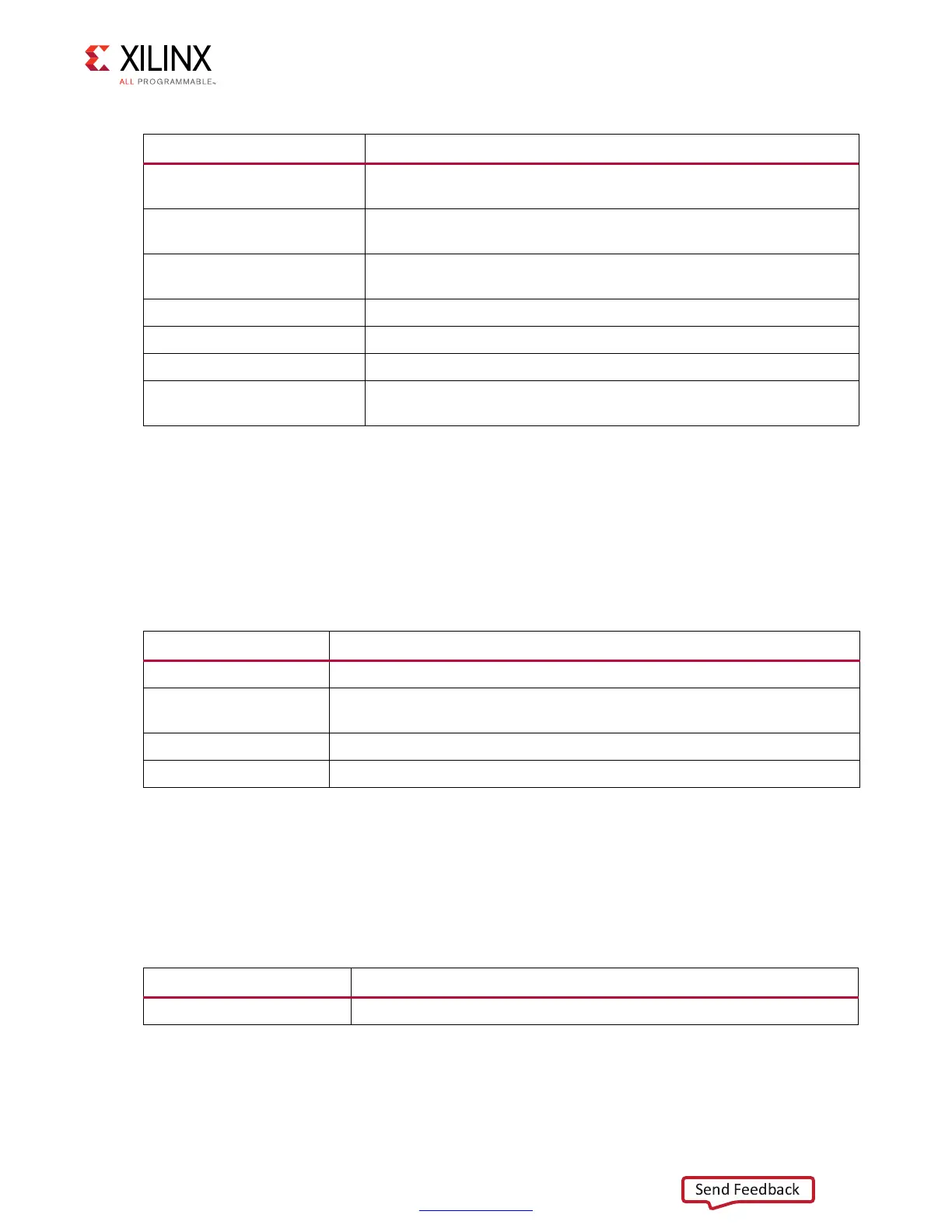

Table 1-10: Files in user_design/xdc Directory

Name Description

<component_name>.xdc This is the XDC for the core and the user design.

Table 1-8: Files in user_design/rtl/phy Directory (Cont’d)

Name

(1)

Description

Loading...

Loading...