Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 285

UG586 November 30, 2016

www.xilinx.com

Chapter 2: QDR II+ Memory Interface Solution

14. Click Next to display the Output Options page.

Customizing and Generating the Core

CAUTION! The Windows operating system has a 260-character limit for path lengths, which can affect

the Vivado tools. To avoid this issue, use the shortest possible names and directory locations when

creating projects, defining IP or managed IP projects, and creating block designs.

MIG Output Options

1. Select Create Design to create a new Memory Controller design. Enter a component

name in the Component Name field (Figure 2-14).

2. Choose the number of controllers to be generated. This selection determines the

replication of further pages.

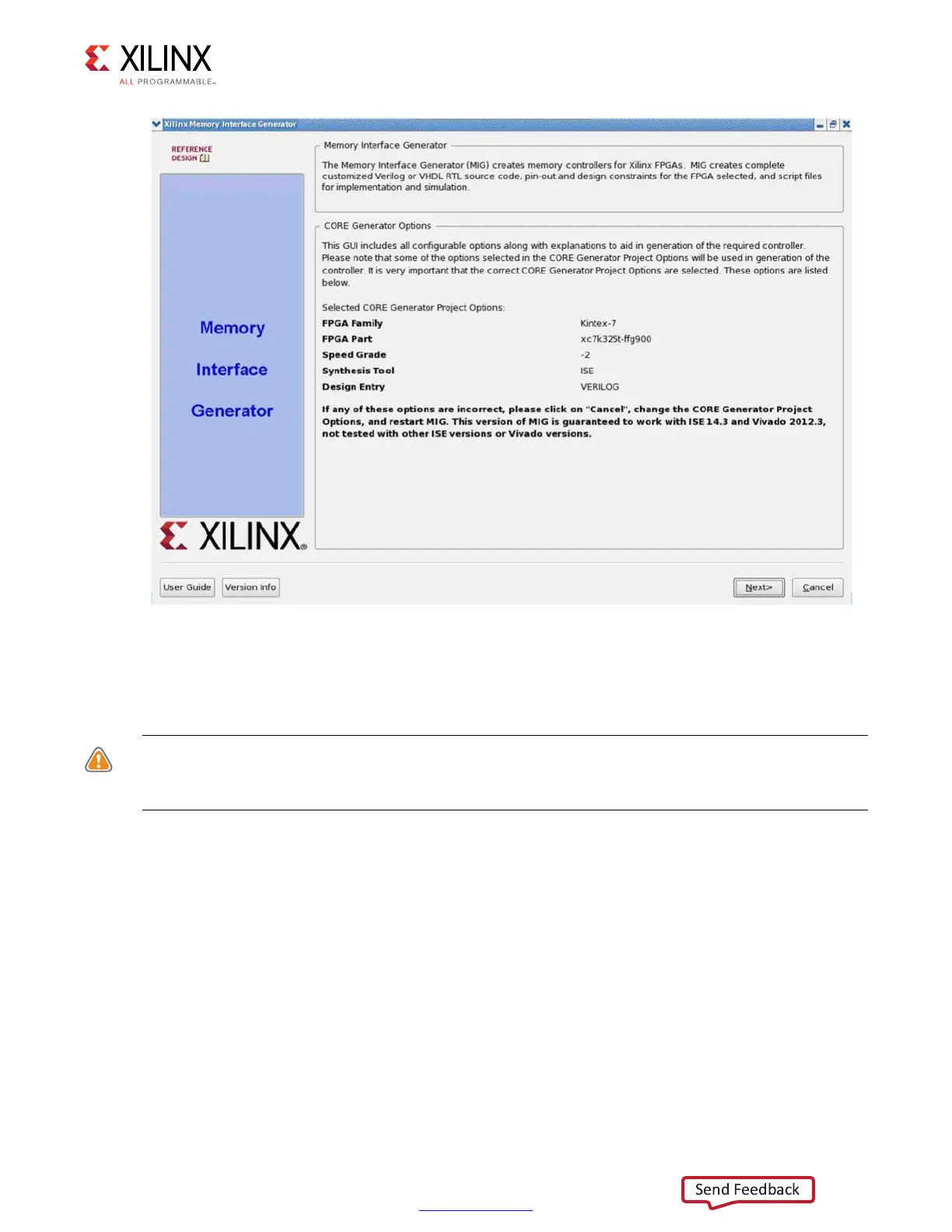

X-Ref Target - Figure 2-13

Figure 2-13: 7 Series FPGAs Memory Interface Generator FPGA Front Page

Loading...

Loading...