Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 420

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

The read data returning from the memory device is accessed by the traffic generator

through the user interface read data port and compared against internally generated

“expect” data. If an error is detected (that is, there is a mismatch between the read data and

expected data), an error signal is asserted and the readback address, readback data, and

expect data are latched into the error_status outputs.

Modifying the Example Design

The provided example_top design comprises traffic generator modules and can be

modified to tailor different command and data patterns. A few high-level parameters can

be modified in the example_top.v/vhd module. Table 3-8 describes these parameters.

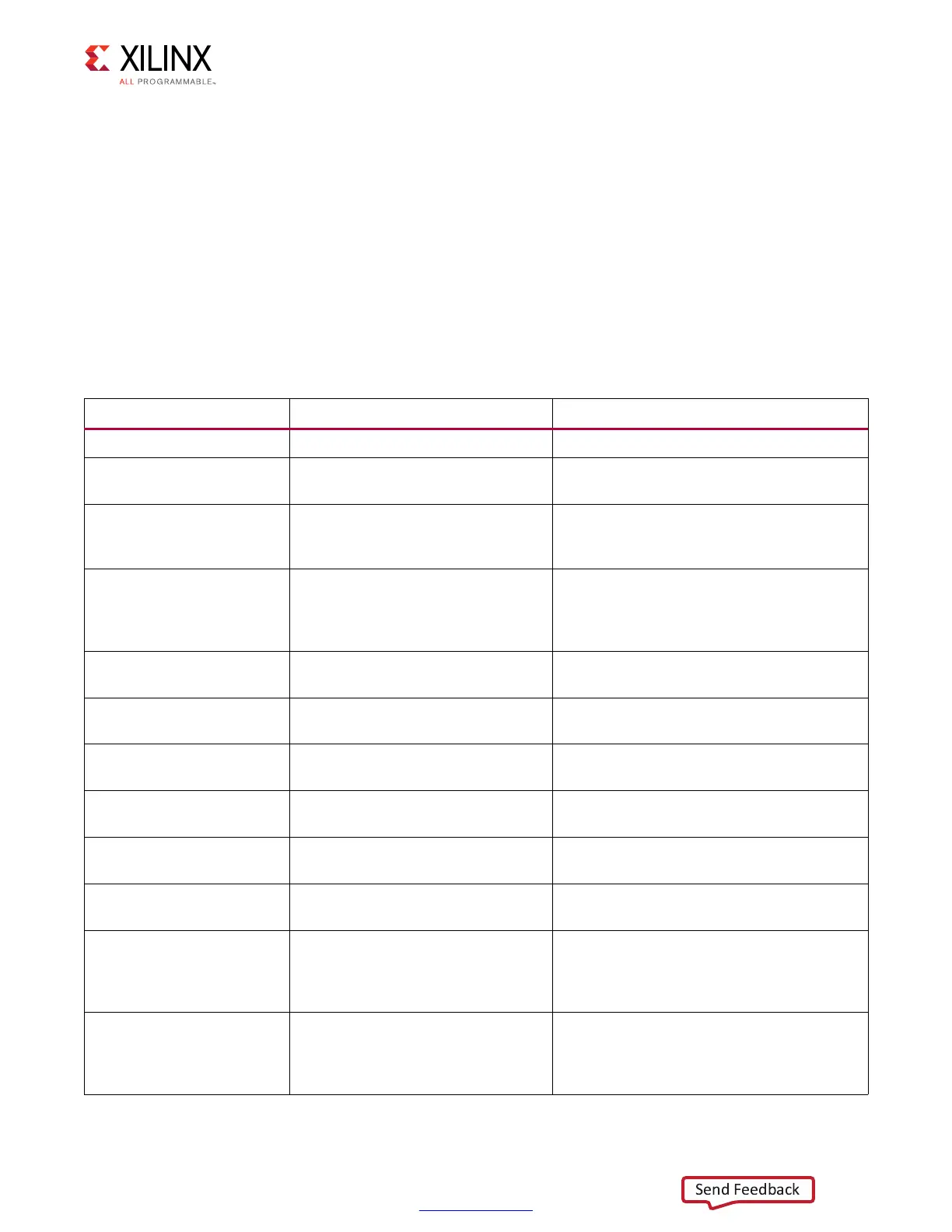

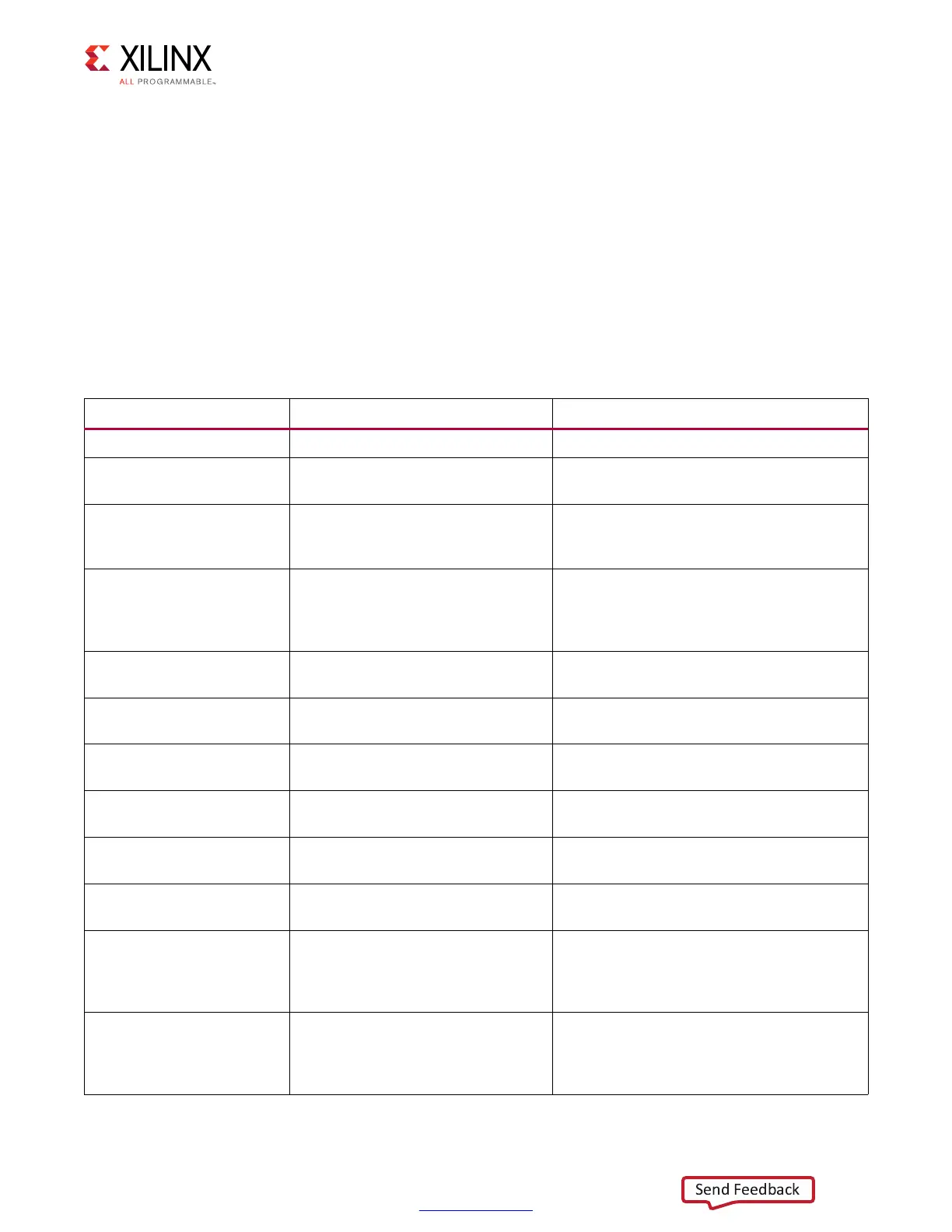

Table 3-8: Traffic Generator Parameters Set in the example_top Module

Parameter Description Value

FAMILY Indicates the family type. “VIRTEX7”

MEMORY_TYPE

Indicate the Memory Controller

type.

Current support is DDR2 SDRAM, DDR3

SDRAM, QDR II+ SRAM, and RLDRAM II.

nCK_PER_CLK

This is the Memory Controller clock

to DRAM clock ratio. This parameter

should not be changed.

RLDRAM II: 2

RLDRAM 3: 4

NUM_DQ_PINS

The is the total memory DQ bus

width.

This parameter supports DQ widths from 8

to a maximum of 72 in increments of 9. The

available maximum DQ width is frequency

dependent on the selected memory device.

MEM_BURST_LEN

This is the memory data burst

length.

This must be set to 8.

MEM_COL_WIDTH

This is the number of memory

column address bits.

This must be set to 10.

DATA_WIDTH

This is the user interface data bus

width.

2 × nCK_PER_CLK × NUM_DQ_PINS

ADDR_WIDTH

This is the memory address bus

width.

MASK_SIZE

This parameter specifies the mask

width in the user interface data bus.

This must be set to DATA_WIDTH/8.

PORT_MODE Sets the port mode.

BI_MODE: Generate a WRITE data pattern

and monitor the READ data for comparison.

BEGIN_ADDRESS

Sets the memory start address

boundary.

This parameter defines the start boundary

for the port address space. The

least-significant Bits[3:0] of this value are

ignored.

END_ADDRESS

Sets the memory end address

boundary.

This parameter defines the end boundary

for the port address space. The

least-significant Bits[3:0] of this value are

ignored.

Loading...

Loading...