Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 142

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Datapath

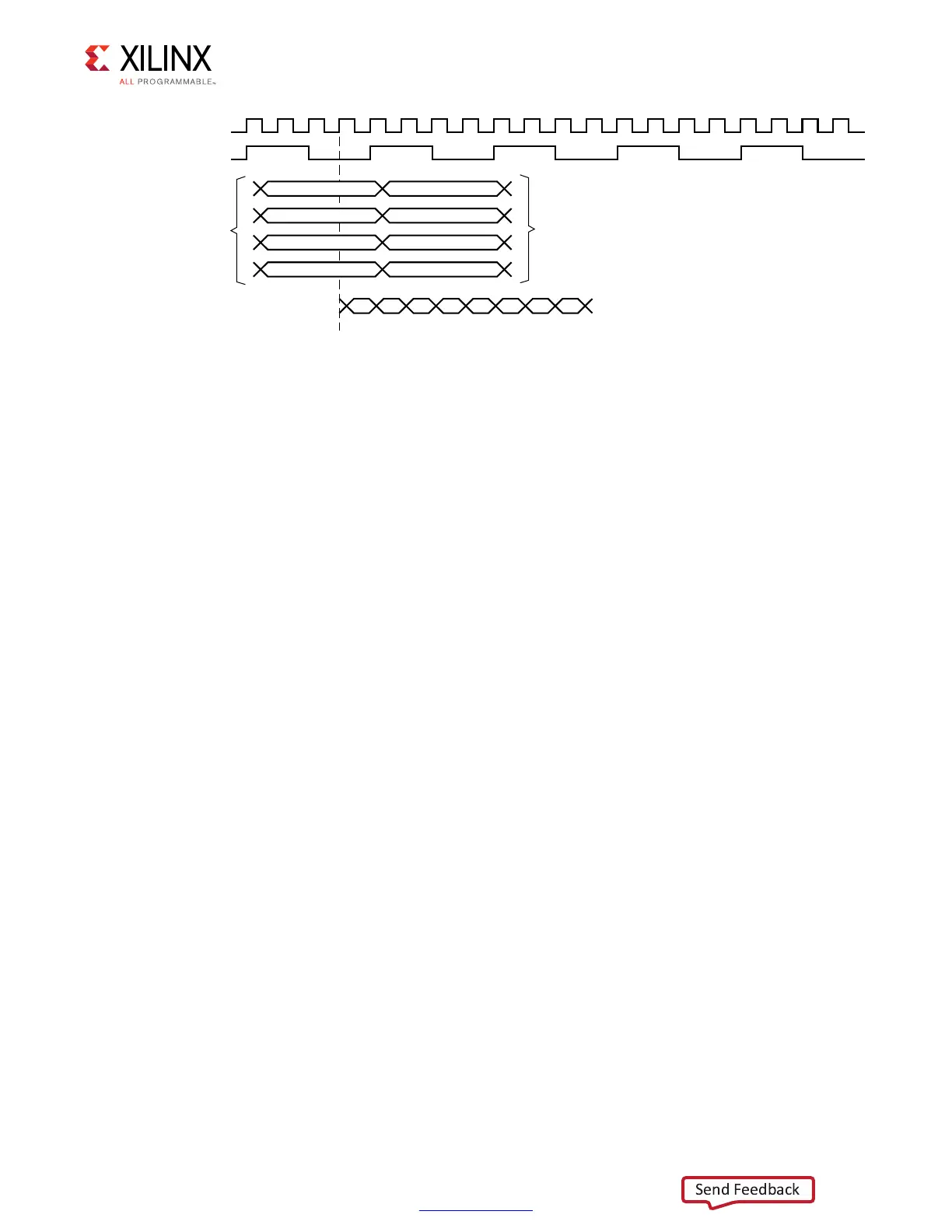

The datapath comprises the write and read datapaths. The datapath in the 7 series FPGA is

completely implemented in dedicated logic with IN/OUT_FIFOs interfacing the FPGA logic.

The IN/OUT_FIFOs provide datapath serialization/deserialization in addition to clock

domain crossing, thereby allowing the FPGA logic to operate at low frequencies up to 1/4

the frequency of the DDR2 or DDR3 SDRAM clock. Figure 1-60 shows the block diagram of

the datapath.

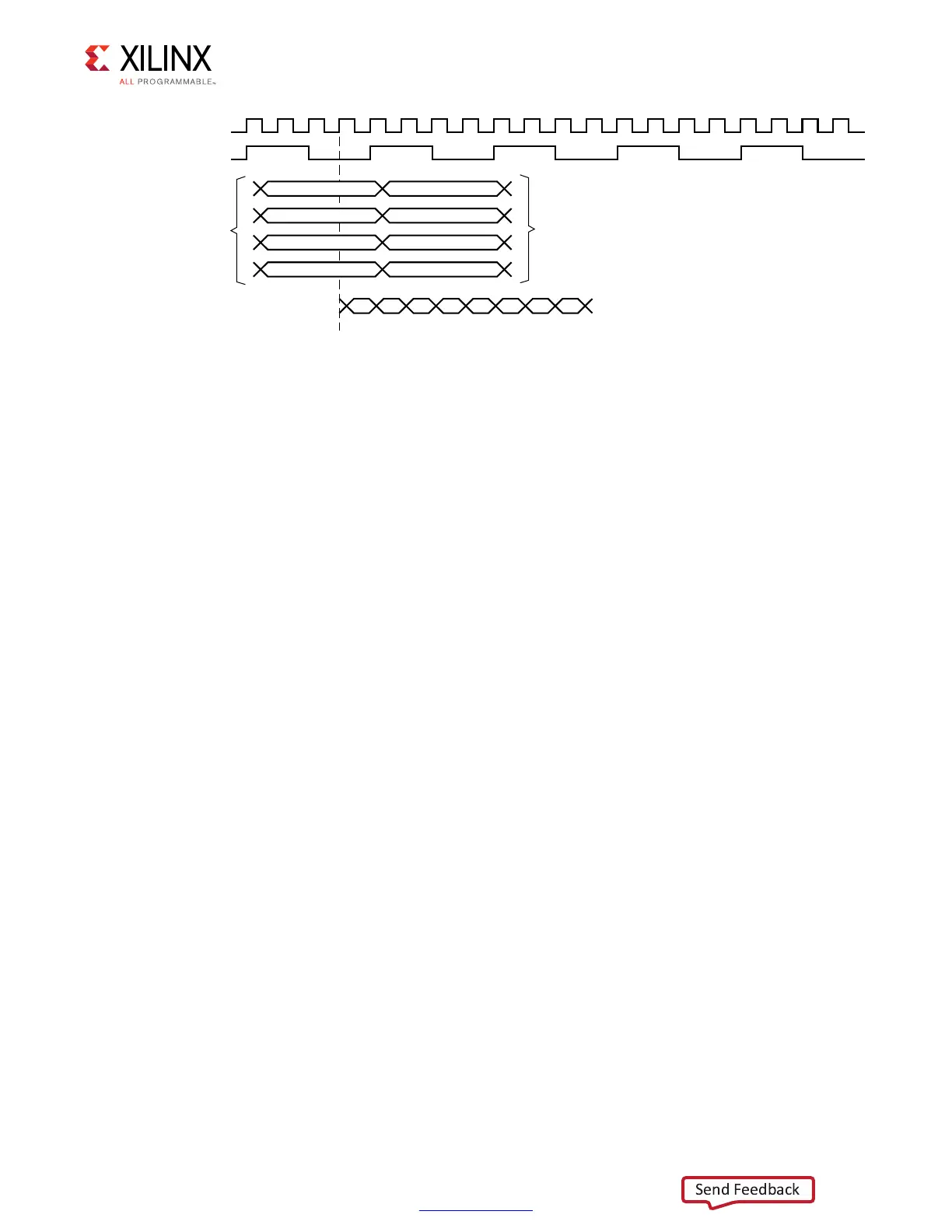

X-Ref Target - Figure 1-59

Figure 1-59: Address/Command Timing Diagram

5'?C??

#,+

#,+$)6

)NPUTSTO/3%2$%3IN3$2

/3%2$%3/UTPUT

#MD #MD

#MD #MD

#MD #MD

#MD

#MD

2!3?.#!3?.7%?.

#3?.!$$2"!

Loading...

Loading...