Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 171

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

A user-refresh operation can be performed any time provided the handshake defined above

is followed. There are no additional interfacing requirements with respect to other

commands. However, pending requests affect when the operation goes out. The Memory

Controller fulfills all pending data requests before issuing the refresh command. Timing

parameters must be considered for each pending request when determining when to strobe

app_ref_req to avoid a tREFI violation. To account for the worst case, subtract tRCD, CL,

the data transit time, and tRP for each bank machine to ensure that all transactions can

complete before tREFI expires. Equation 1-1 shows the REF request interval maximum.

Equation 1-1

A user REF should be issued immediately following calibration to establish a time baseline

for determining when to send subsequent requests.

User ZQ

For user-controlled ZQ calibration, the Memory Controller managed maintenance should

be disabled by setting the tZQI parameter to 0.

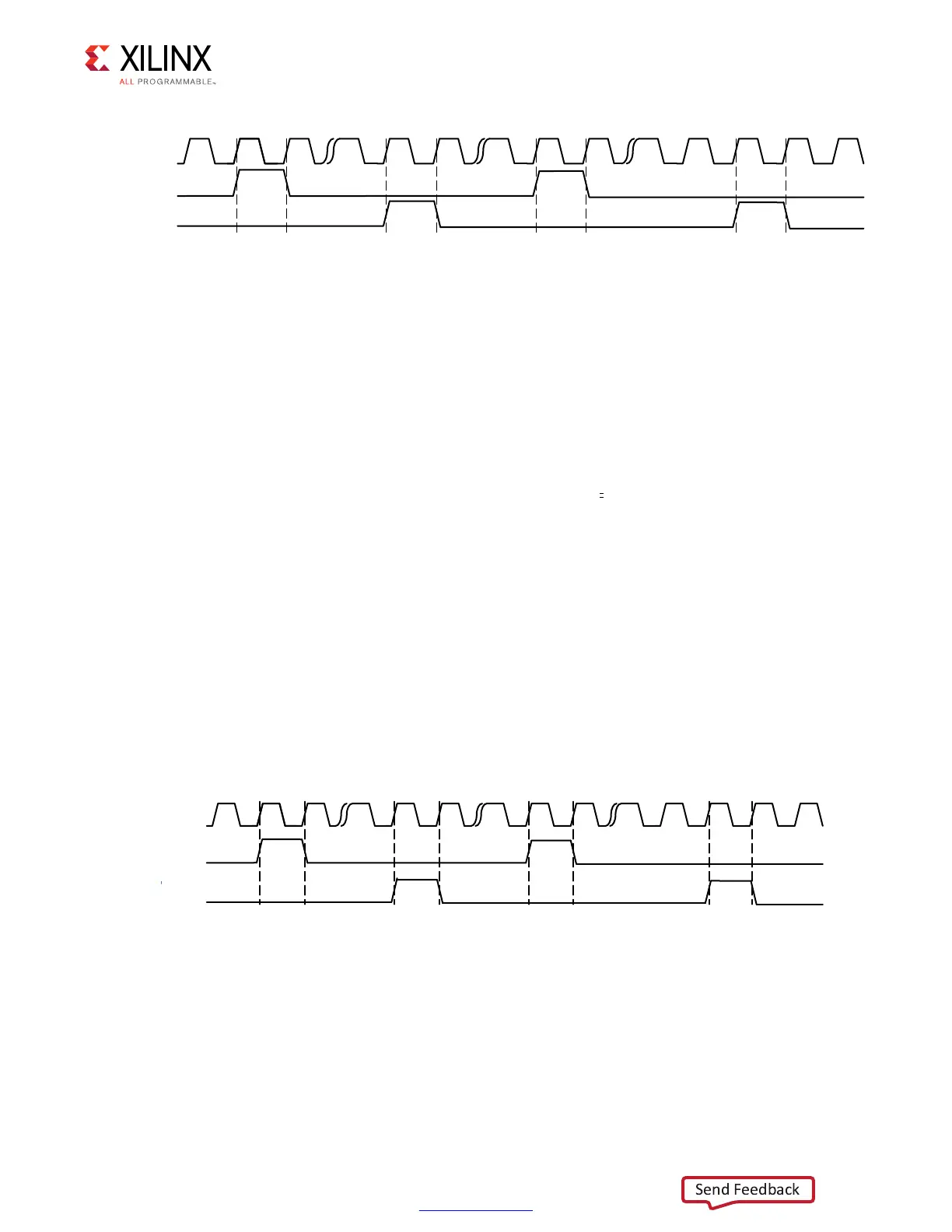

To request a ZQ command, app_zq_req is strobed for one cycle. When the Memory

Controller sends the command to the PHY, it strobes app_zq_ack for one cycle, after

which another request can be sent. Figure 1-84 illustrates the interface.

A user ZQ operation can be performed any time provided the handshake defined above is

followed. There are no additional interfacing requirements with respect to other commands.

However, pending requests affect when the operation goes out. The Memory Controller

fulfills all pending data requests before issuing the ZQ command. Timing parameters must

be considered for each pending request when determining when to strobe app_zq_req to

achieve the desired interval if precision timing is desired.

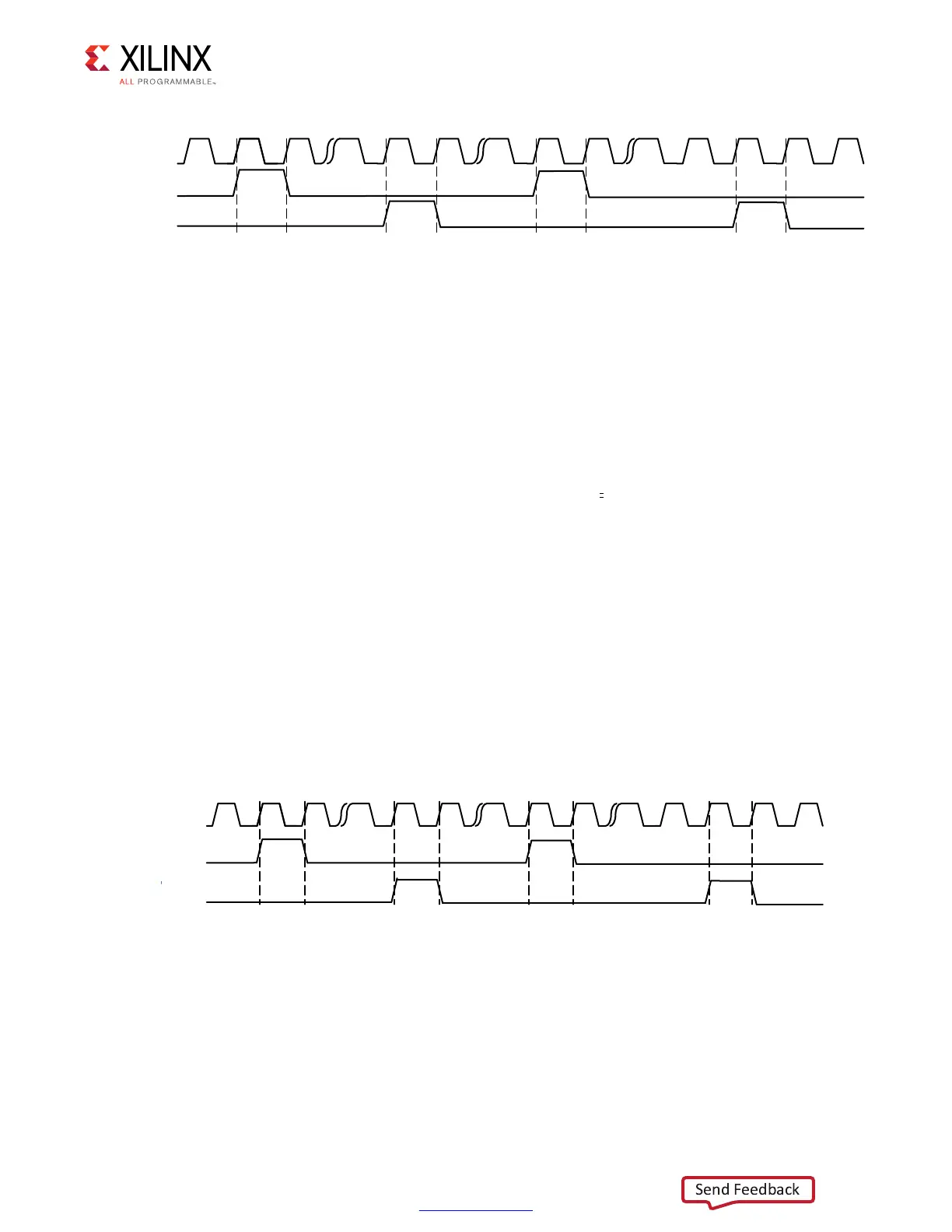

X-Ref Target - Figure 1-83

Figure 1-83: User-Refresh Interface

CLK

APP?REF?REQ

APP?REF?ACK

8

tREFI tRCD CL 4+()tCK×()+ tRP+()nBANK_MACHS×–()

X-Ref Target - Figure 1-84

Figure 1-84: User ZQ Interface

CLK

APP?ZQ?REQ

APP?ZQ?ACK

8

Loading...

Loading...