Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 254

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

•Two CK early write pattern read back – 55AA9966BB11EE44

•One CK late write pattern read back – XXXXFF00AA5555AA

°

Calibration cannot correct for this pattern. This pattern indicates that the trace

delays are incorrect where CK is incorrectly shorter than DQS.

If none of the above patterns are detected during reads, the algorithm assumes the MPR

read leveling IDELAY settings are incorrect and the IDELAYs for the DQ bits associated with

that byte are set to 0. MPR read leveling could have an incorrect IDELAY setting because

with the “01010101” or “10101010” pattern, it is not possible to differentiate between clock

cycles.

Debug

If dbg_wrcal_err is asserted, denoting a Write Calibration failure, use dbg_wrcal_err

= R as the trigger and observe the following debug signals. If dbg_wrcal_done asserted

but the results of this stage need to be analyzed, use dbg_wrcal_done as the trigger.

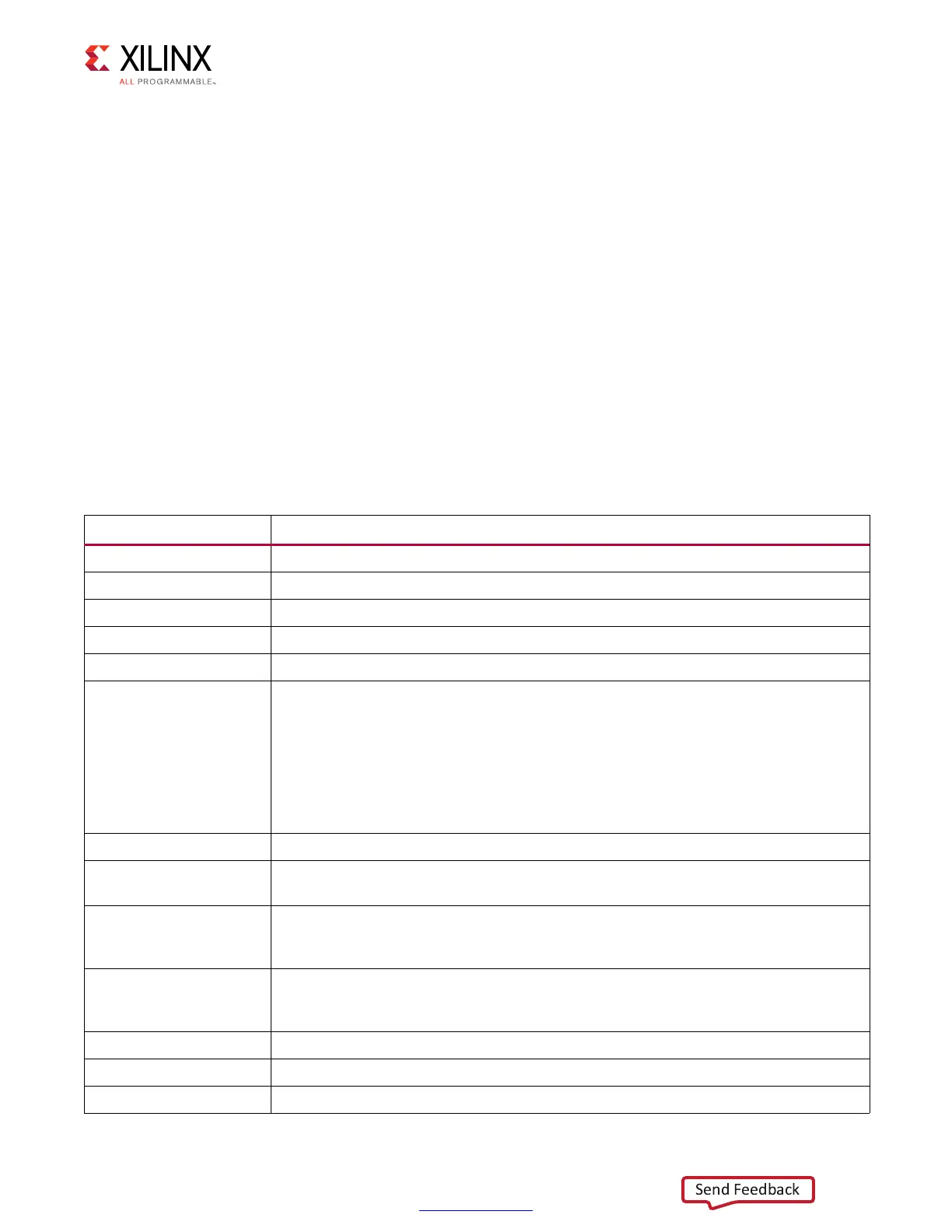

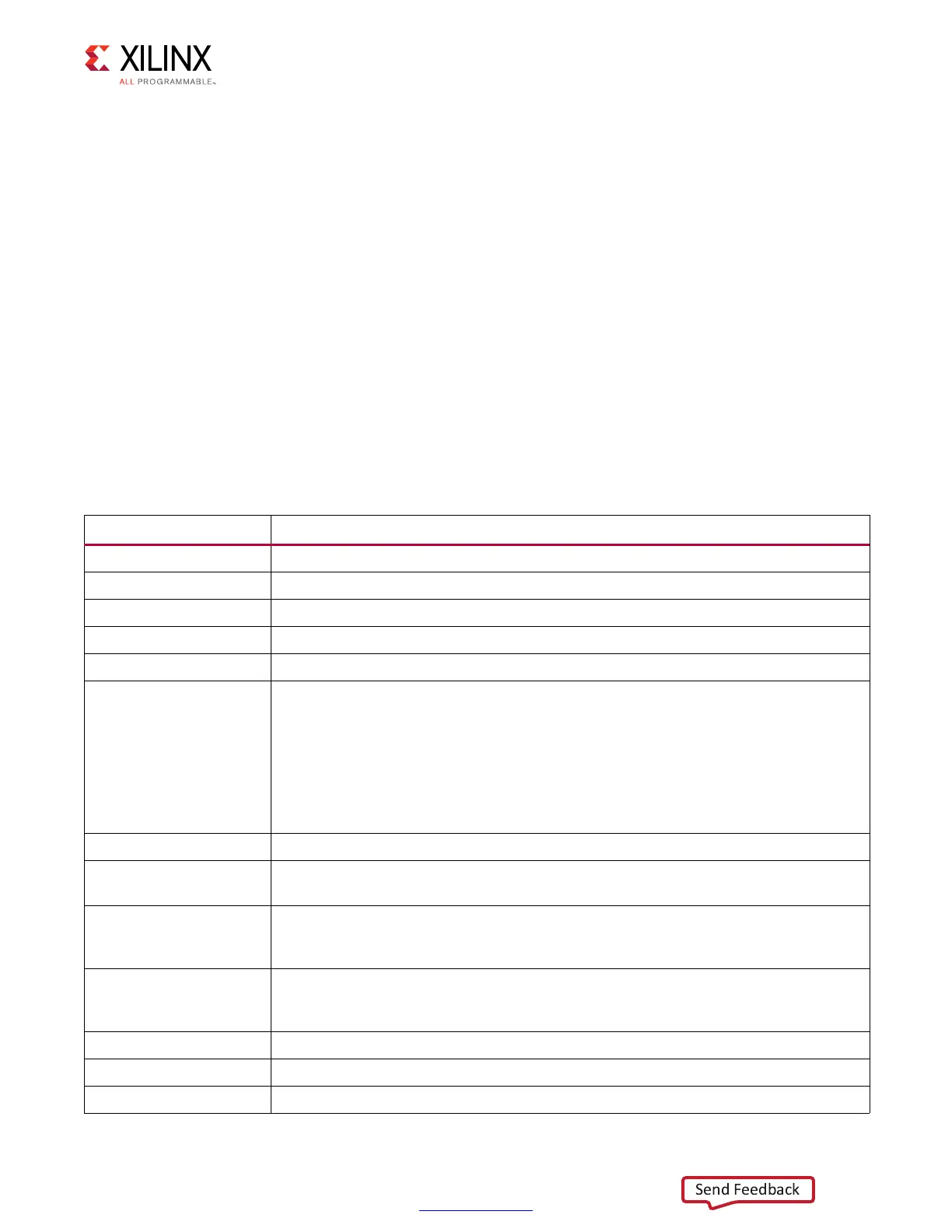

Table 1-79: Debug Signals of Interest for Write Calibration

Signal Name Description

dbg_wrcal_start Signifies the start of the Write Calibration stage of calibration.

dbg_wrcal_done Signifies successful completion of the Write Calibration stage of calibration.

dbg_wrcal_err Signifies Write Calibration exhibited errors and did not complete.

pat_data_match Asserts when the valid pattern is detected.

pat_data_match_valid Toggles when the correct pattern is detected.

wrcal_dqs_cnt

Current DQS group being calibrated in Write Calibration. When dbg_wrcal_start

asserts, wrcal_dqs_cnt is 0. The algorithm sequentially steps through the DQS byte

groups checking to see if the read data pattern matches the expected

FF00AA5555AA9966 pattern. If the pattern matches, wrcal_dqs_cnt increments by 1.

The algorithm then starts looking for the correct data pattern on the next byte until

it reaches DQS_WIDTH – 1 or a data byte group fails due to the data pattern not being

detected properly. The wrcal_dqs_cnt stays at DQS_WIDTH – 1 after dbg_wrcal_done

signal is asserted.

cal2_state Write Calibration state machine variable.

not_empty_wait_cnt

Count value during write calibration pattern detection. Maximum count is 0x1F. If

count reaches 0x1F, write calibration fails with the assertion of dbg_wrcal_err.

early1_data

Asserts when the pattern detected is one CK clock cycle early. When this is asserted,

the write leveling algorithm moves the CK clock one cycle. After CK is moved, the write

calibration algorithm restarts pattern detection.

early2_data

Asserts when the pattern detected is two CK clock cycles early. When this is asserted,

the write leveling algorithm moves the CK clock two cycles. After CK is moved, the

write calibration algorithm restarts pattern detection.

dbg_wcal_mux_rd_rise0_r Data pattern received on rising edge 0.

dbg_wcal_mux_rd_fall0_r Data pattern received on falling edge 0.

dbg_wcal_mux_rd_rise1_r Data pattern received on rising edge 1.

Loading...

Loading...