Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 270

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

• Check the IDELAY values after calibration. Look for variations between IDELAY values.

IDELAY values should be very similar for DQs in the same DQS group.

• For debugging purposes only, vary the IDELAY taps after calibration for the bits that are

returning bad data.

Checking and Varying Read Timing

Debug signals are provided to verify read window margin on a per-byte basis and should be

used for debugging purposes only. Determining if sufficient margin is available for reliable

operation can be useful for debugging purposes if data errors are seen after calibration.

There is an automated window check flow that can be used to step through the entire

interface and provides the # of PHASER taps required to reach the left edge and right edge

of the data window. The window checking can also be manually verified by manually

incrementing and decrementing the PHASER taps to verify how much window margin is

available.

Automated Window Check

The automated window checking is enabled by asserting win_start with a single pulse.

win_active should then assert until all byte groups have been measured.

win_sel_pi_pon must be set to 0x1 to enable Read window measurement. and

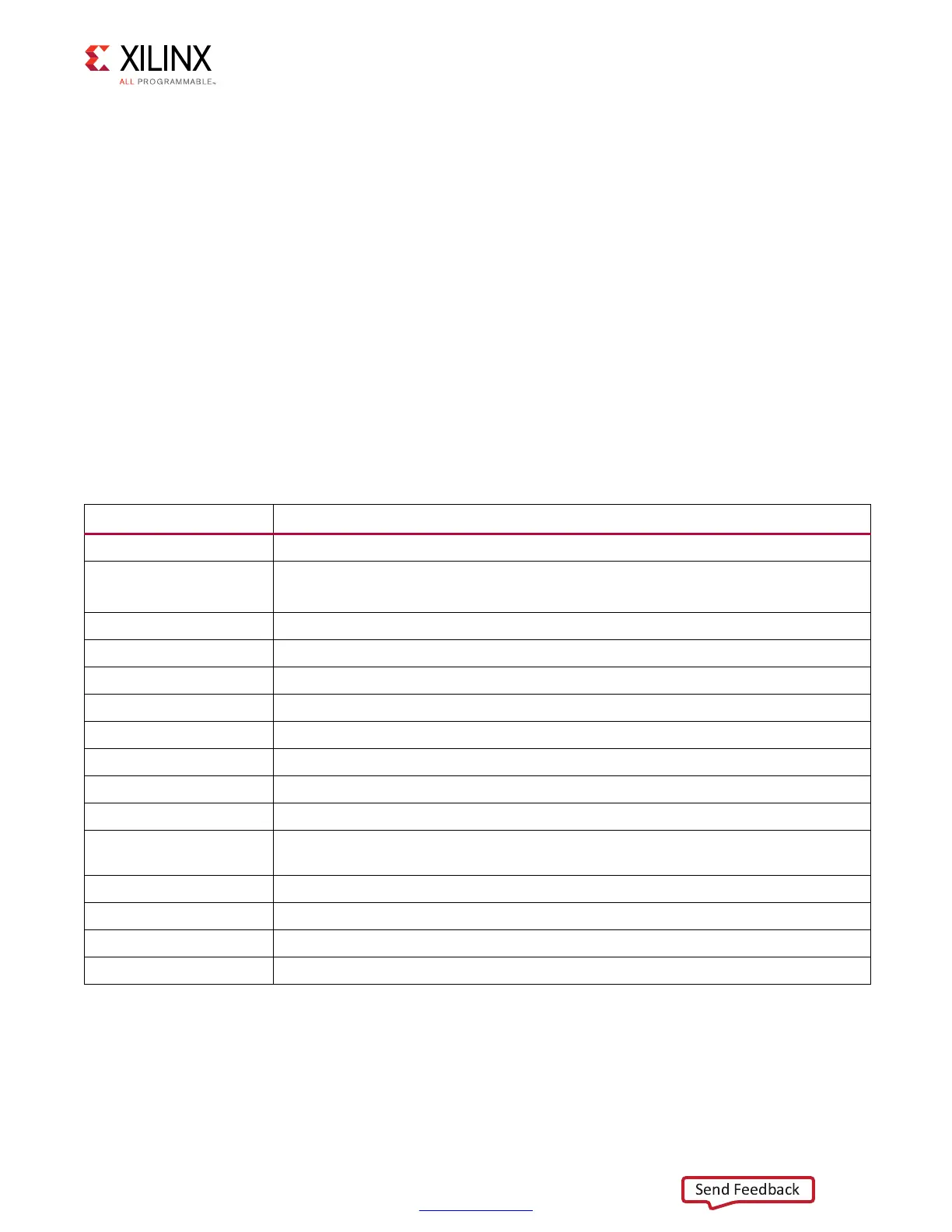

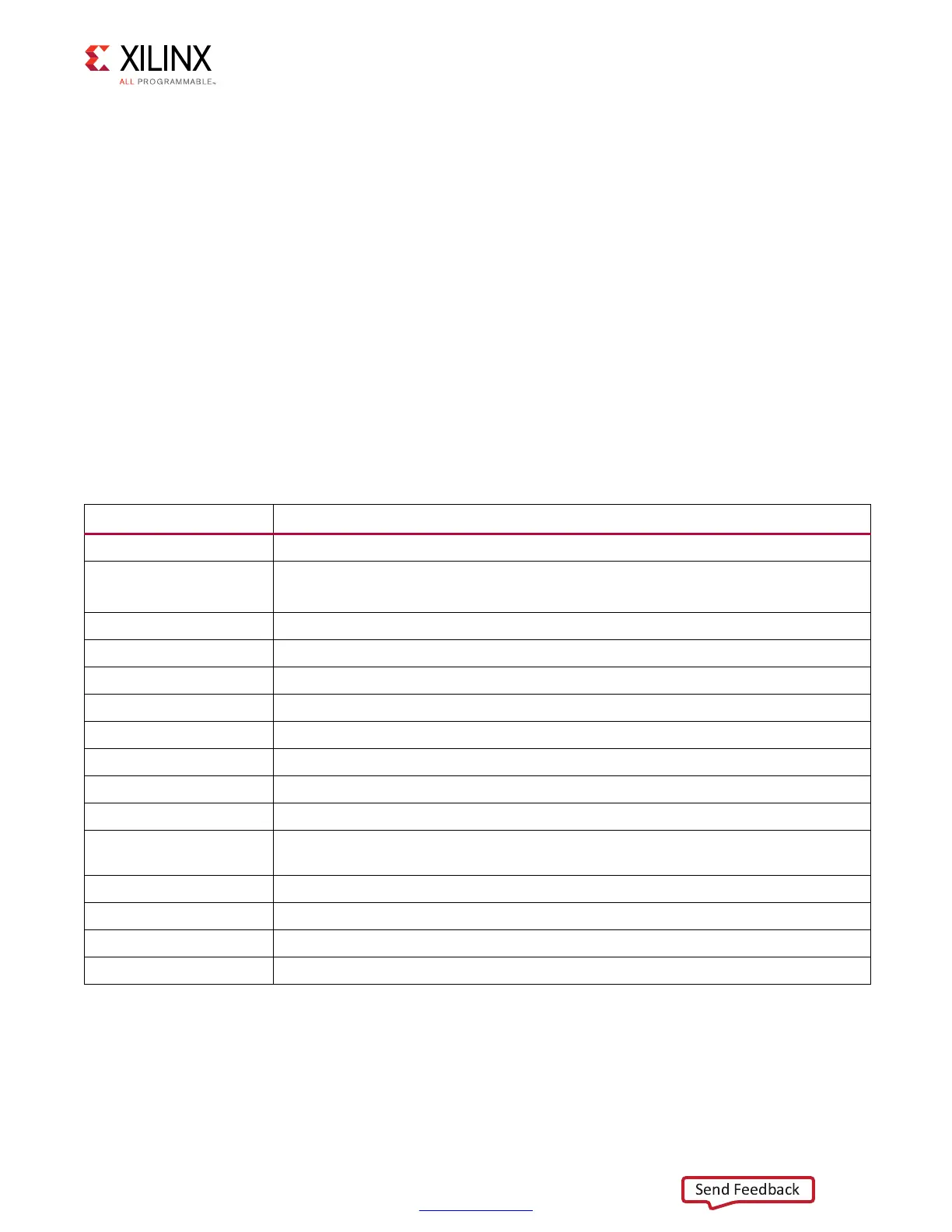

Table 1-85: Debug Signals Used for Checking and Varying Read/Write Timing

Signal Name Description

win_start Single pulse that starts the window check logic.

win_sel_pi_pon

Controls window check logic on read path. Valid settings are:

• 0x1 = Enables Read Path

vio_dbg_sel_pi_incdec Enables manual incrementing and decrementing of the PHASER_IN taps.

vio_dbg_pi_f_inc Increments PHASER_IN fine taps when win_sel_pi_pon = 0x1.

vio_dbg_pi_f_dec Decrements PHASER_IN fine taps when win_sel_pi_pon = 0x1.

vio_win_byte_select_inc Increments the byte group being checked by the window margin check module.

vio_win_byte_select_dec Decrements the byte group being checked by the window margin check module.

dbg_pi_counter_read_val Current PHASER_IN tap count corresponding to current byte being checked.

pi_win_left_ram_out PHASER_IN tap count to reach the left edge of the read window for a given byte.

pi_win_right_ram_out PHASER_IN tap count to reach the right edge of the read window for a given byte.

win_active

Flag to indicate the Window check logic is active and measuring window margins.

While active, the other VIOs should not be changed.

win_current_byte Feedback to indicate which byte is currently being monitored.

win_byte_select Selects which byte group to display the measured results for.

dbg_clear_error Clears error in Traffic Generator as a result of changing tap values.

vio_sel_mux_rdd[3:0] Selects the byte for which the phaser increments or decrements are applied.

Loading...

Loading...