Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 73

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

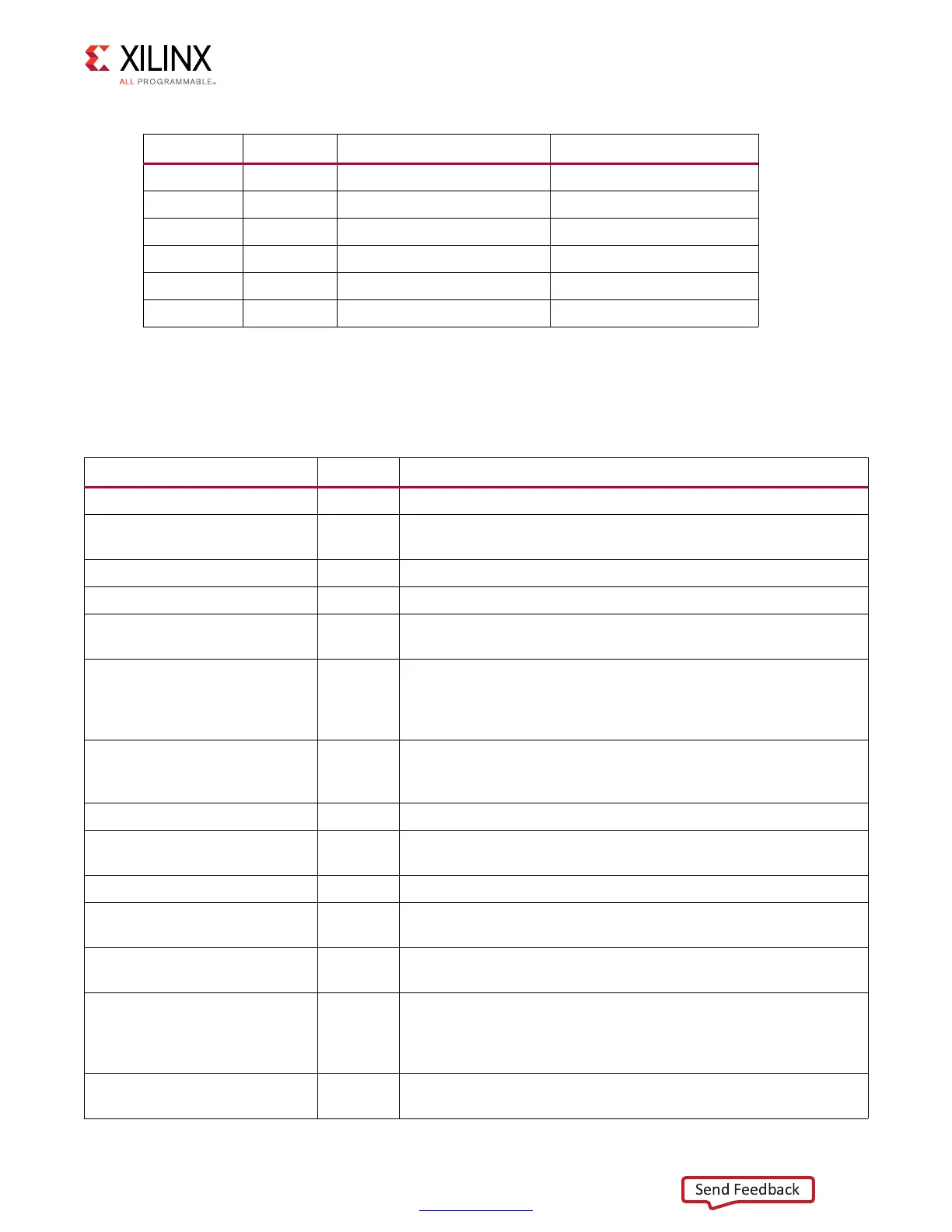

Traffic Generator Signal Description

Traffic generator signals are described in Table 1-13.

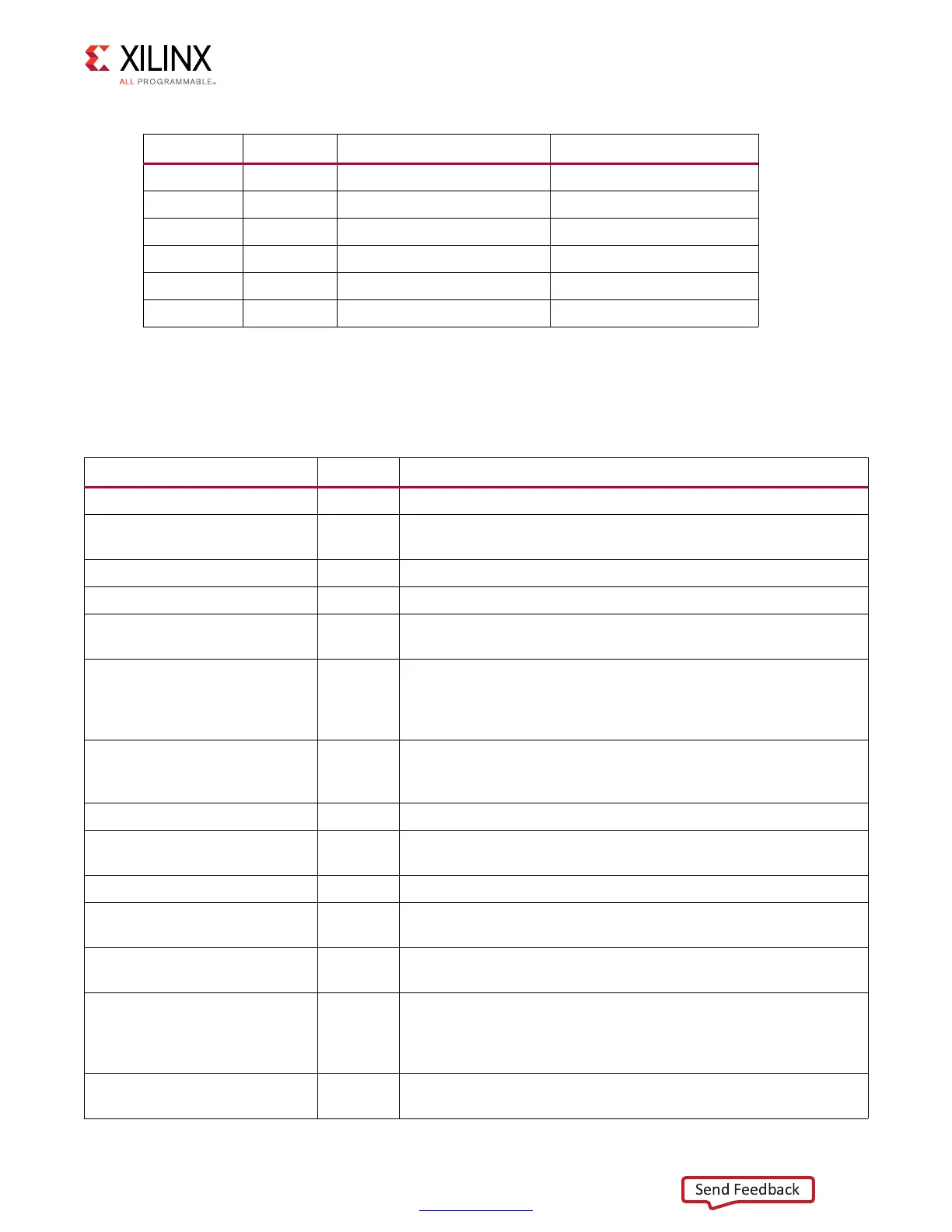

0x2000 0xAFFF 0x00002000 0xFFFF0000

0x2000 0xBFFF 0x00002000 0xFFFF0000

0x2000 0xCFFF 0x00002000 0xFFFF0000

0x2000 0xDFFF 0x00002000 0xFFFF0000

0x2000 0xEFFF 0x00002000 0xFFFF0000

0x2000 0xFFFF 0x00002000 0xFFFF0000

Table 1-12: Example Settings for Address Space and PRBS Masks (Cont’d)

SADDR EADDR PRBS_SADDR_MASK_POS PRBS_EADDR_MASK_POS

Table 1-13: Traffic Generator Signal Descriptions

Signal Direction Description

clk_i Input This signal is the clock input.

memc_init_done Input

This is the input status signal from the Memory Controller to

indicate that it is ready accept traffic.

manual_clear_error Input Input signal to clear error flag.

memc_cmd_addr_o[31:0] Output Start address for current transaction.

memc_cmd_en_o Output

This active-High signal is the write-enable signal for the Command

FIFO.

memc_cmd_full_i Input

This connects to inversion of app_rdy of Memory Controller. When

this input signal is asserted, TG continues to assert the

memc_cmd_en_o, memc_cmd_addr_o value and memc_cmd_instr

until the memc_cmd_full_i is deasserted.

memc_cmd_instr[2:0] Output

Command code for current instruction.

Command Write: 3'b000

Command Read: 3'b001

memc_rd_data_i[DWIDTH – 1:0] Input Read data value returning from memory.

memc_rd_empty_i Input

This active-High signal is the empty flag for the Read Data FIFO in

Memory Controller. It indicates there is no valid data in the FIFO.

memc_rd_en_o Output This signal is only used in MCB-like interface.

memc_wr_data_o[DWIDTH –

1:0]

Output

Write data value to be loaded into Write Data FIFO in Memory

Controller.

memc_wr_en_o Output

This active-High signal is the write enable for the Write Data FIFO.

It indicates that the value on memc_wr_data is valid.

memc_wr_full_i Input

This active-High signal is the full flag for the Write Data FIFO from

Memory Controller. When this signal is High, TG holds the write

data value and keeps assertion of memc_wr_en until the

memc_wr_full_i goes Low.

qdr_wr_cmd_o Output

This signal is only used to send write commands to the QDR II+

user interface.

Loading...

Loading...