Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 357

UG586 November 30, 2016

www.xilinx.com

Chapter 2: QDR II+ Memory Interface Solution

4. In the Flow Navigator window, select Run Simulation and select Run Behavioral

Simulation as shown in Figure 2-51.

5. Vivado invokes Questa Advanced Simulator and simulations are run in the Questa

Advanced Simulator tool. For more information, see the Vivado Design Suite User Guide:

Logic Simulation (UG900) [Ref 8].

Simulation Flow Using VCS

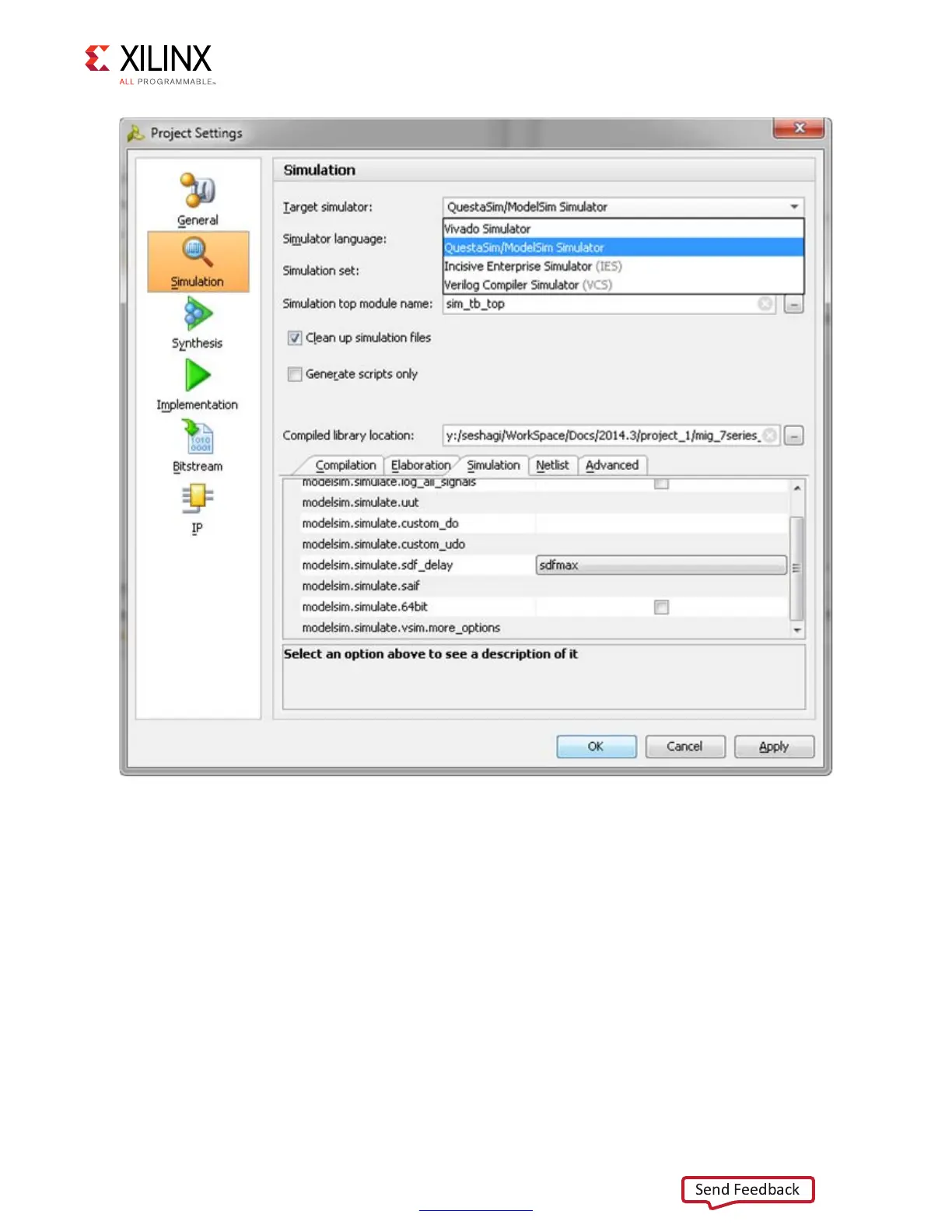

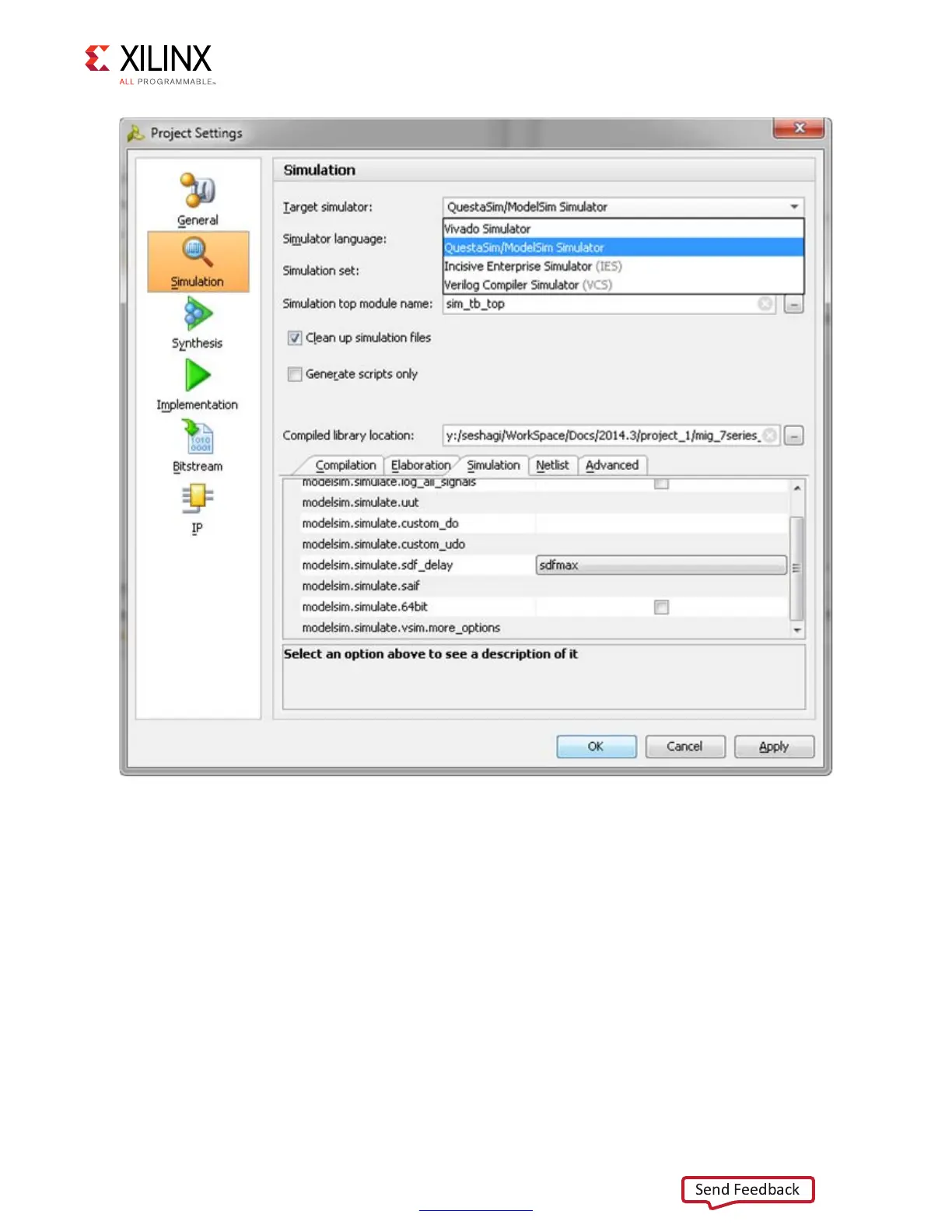

1. In the Open IP Example Design Vivado project, under Flow Navigator select

Simulation Settings.

2. Select Target simulator as Verilog Compiler Simulator (VCS).

X-Ref Target - Figure 2-52

Figure 2-52: Simulation with Questa Advanced Simulator

Loading...

Loading...