Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 362

UG586 November 30, 2016

www.xilinx.com

Chapter 2: QDR II+ Memory Interface Solution

Calibration

Calibration completes read leveling, write calibration, and read enable calibration. This is

completed over two stages. This sequence successfully completes when the cal_done

signal is asserted. For more details, see Physical Interface, page 324.

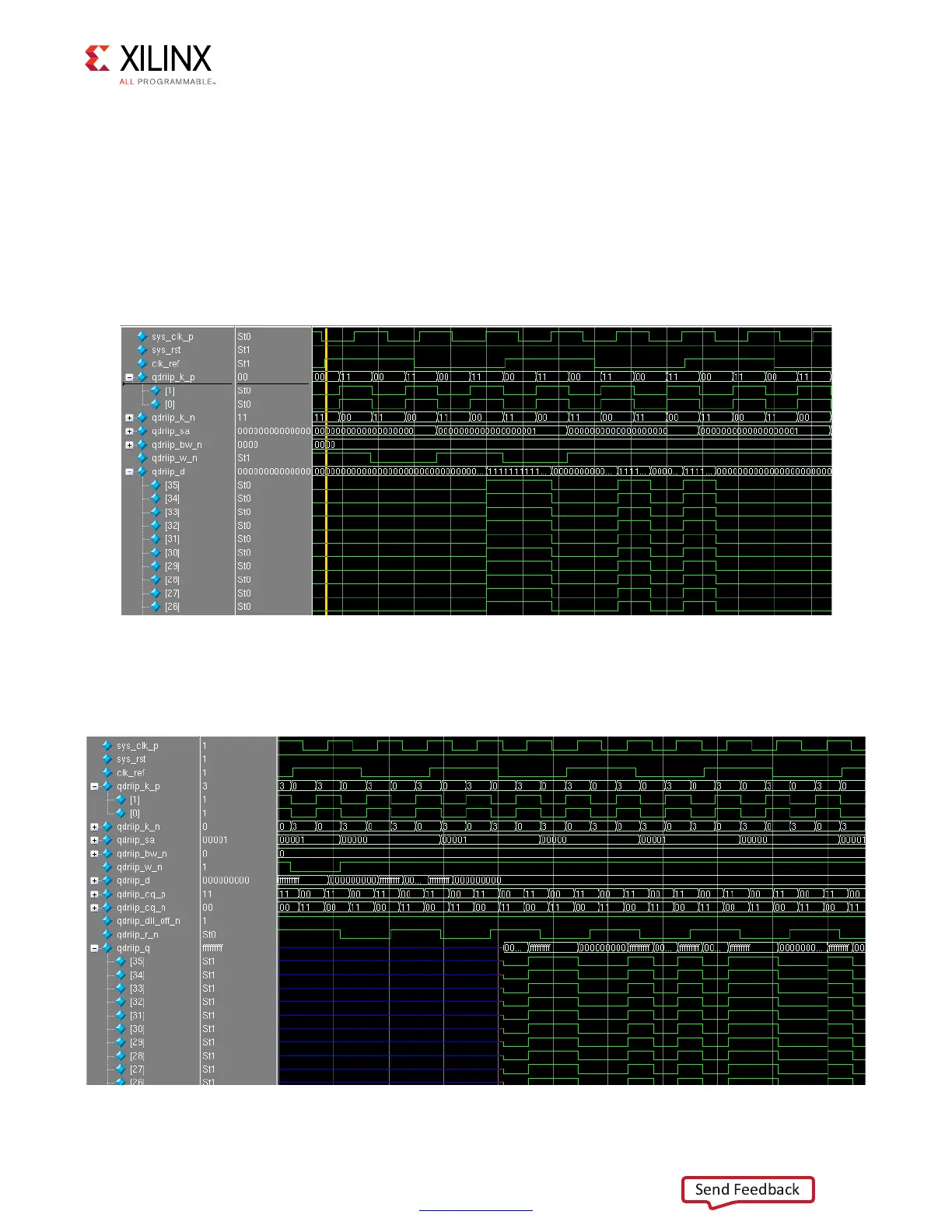

The first stage performs per-bit read leveling calibration. The data pattern used during this

stage is 00FF00FF00FFFF00. The data pattern is first written to the memory, as shown in

Figure 2-55.

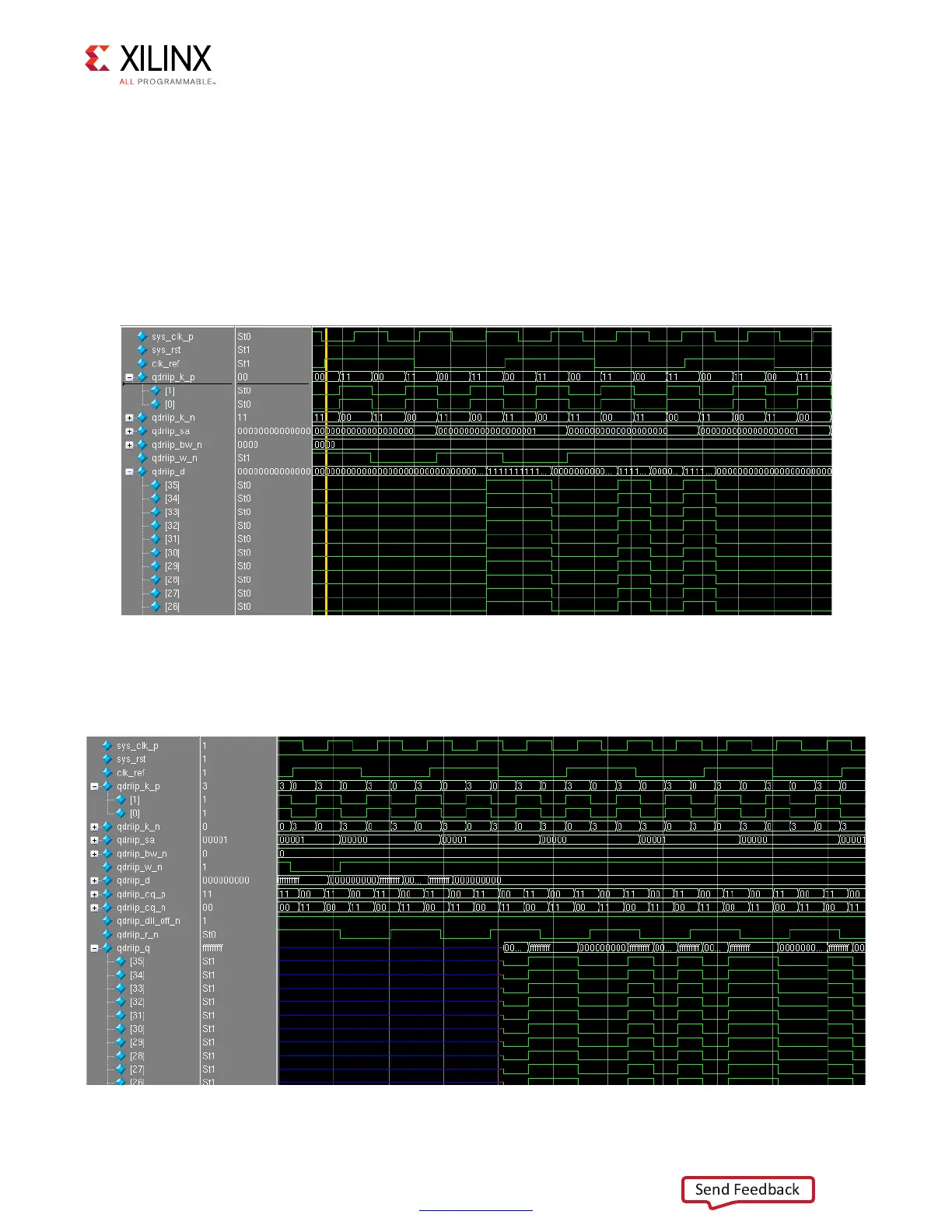

This pattern is then continuously read back while the per-bit calibration is completed, as

shown in Figure 2-56.

X-Ref Target - Figure 2-55

Figure 2-55: Writes for First Stage Read Calibration

X-Ref Target - Figure 2-56

Figure 2-56: Reads for First Stage Read Calibration

Loading...

Loading...