Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 21

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Using MIG in the Vivado Design Suite

This section provides the steps to generate the Memory Interface Generator (MIG) IP core

using the Vivado Design Suite and run implementation.

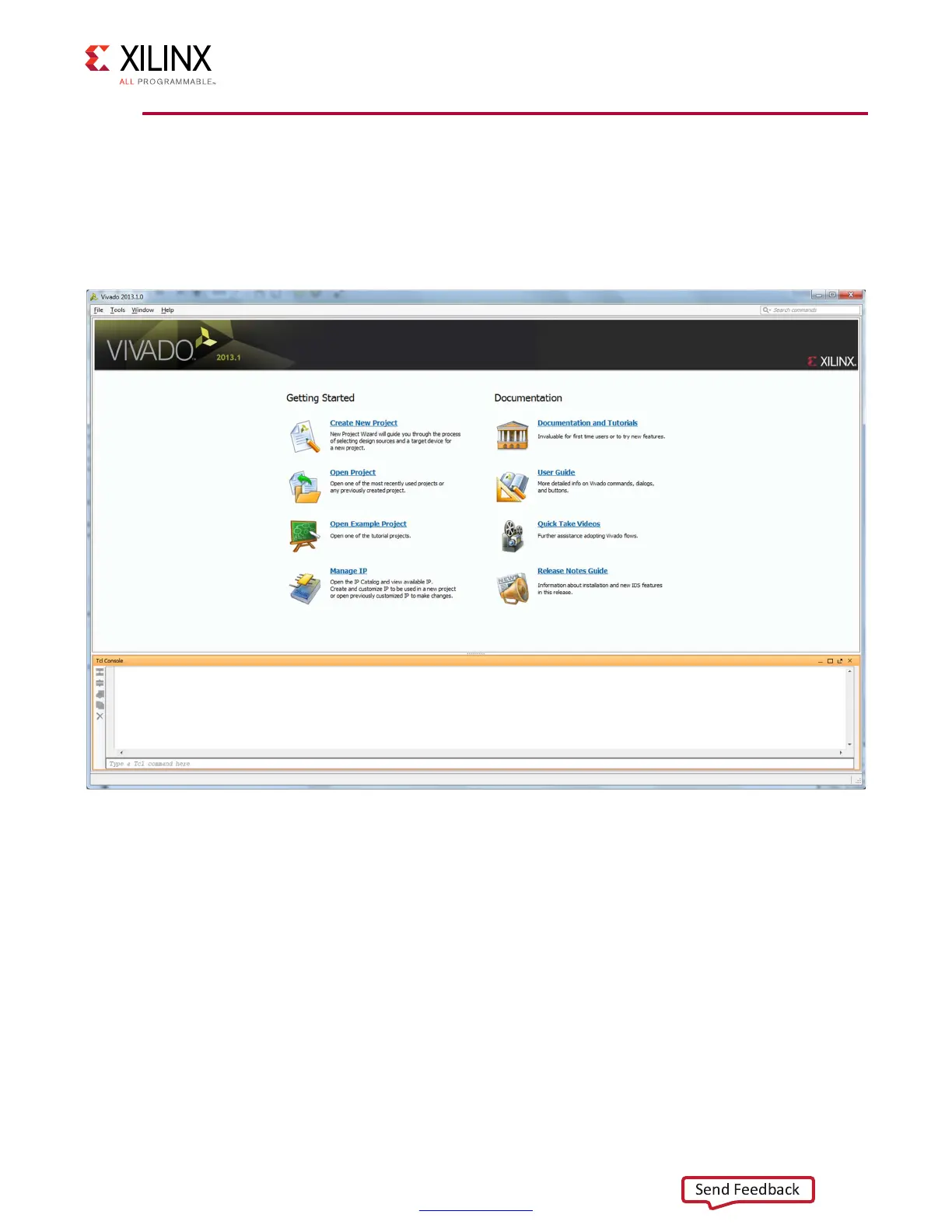

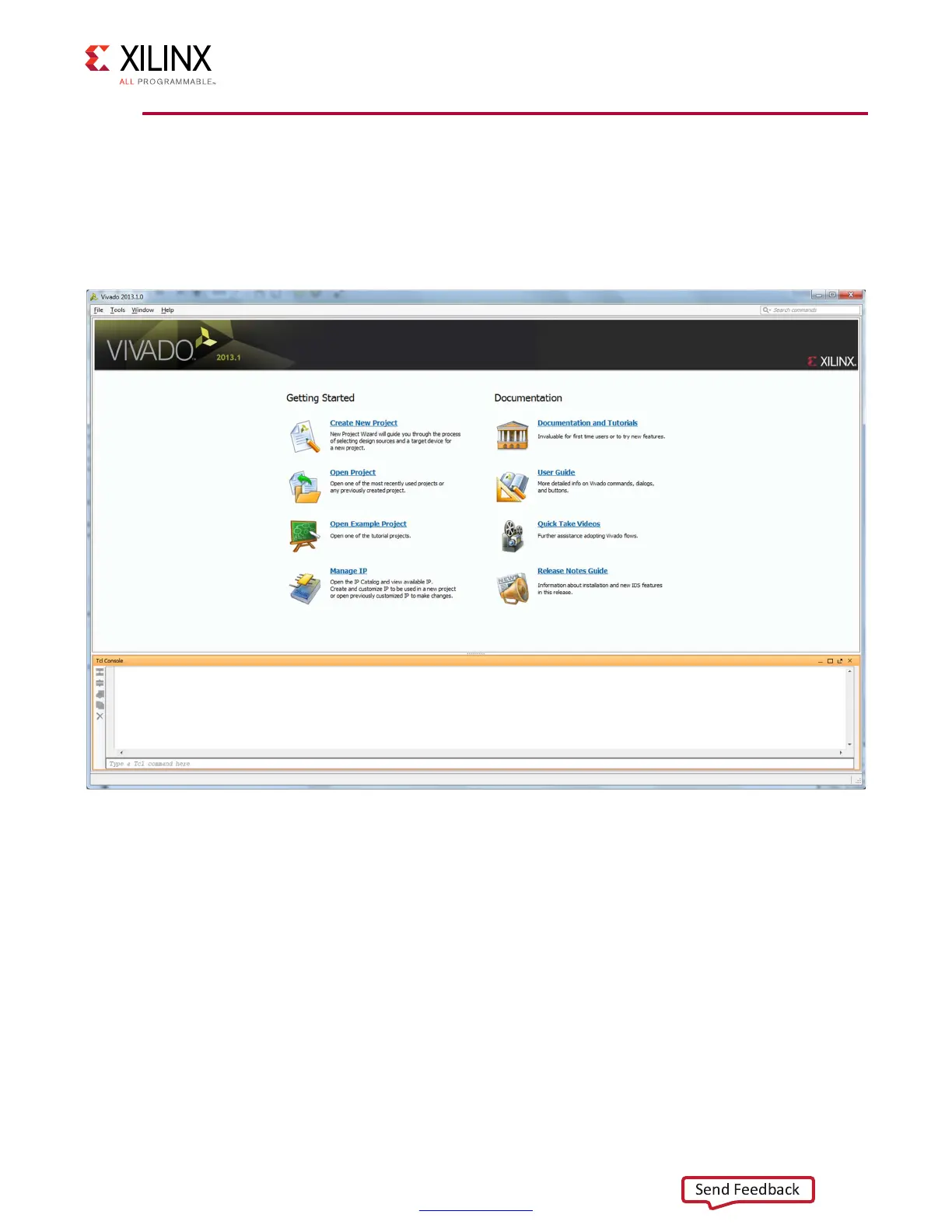

1. Start the Vivado Design Suite (see Figure 1-1).

2. To create a new project, click the Create New Project option shown in Figure 1-1 to

open the page as shown in Figure 1-2.

X-Ref Target - Figure 1-1

Figure 1-1: Vivado Design Suite

Loading...

Loading...