Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 295

UG586 November 30, 2016

www.xilinx.com

Chapter 2: QDR II+ Memory Interface Solution

I/O Planning Options

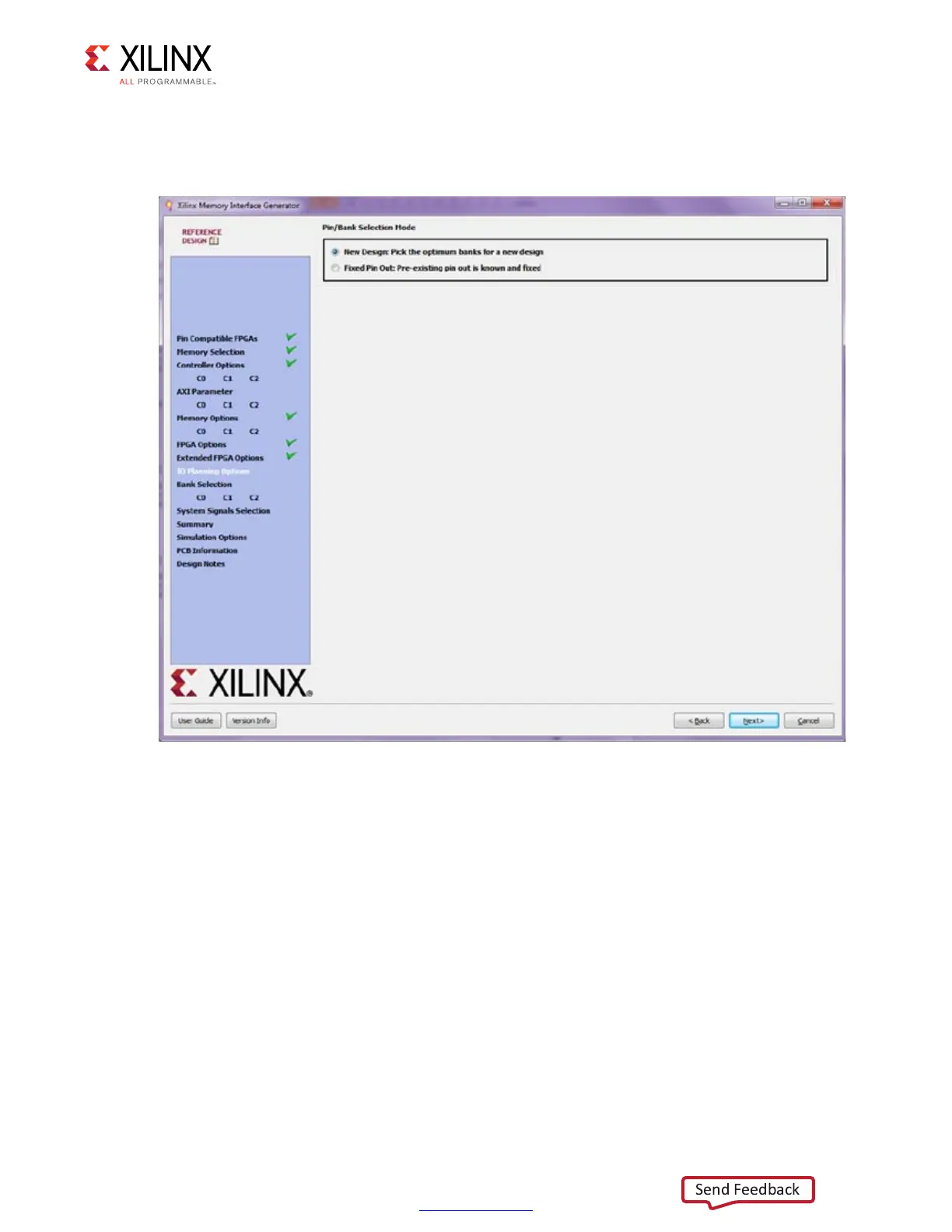

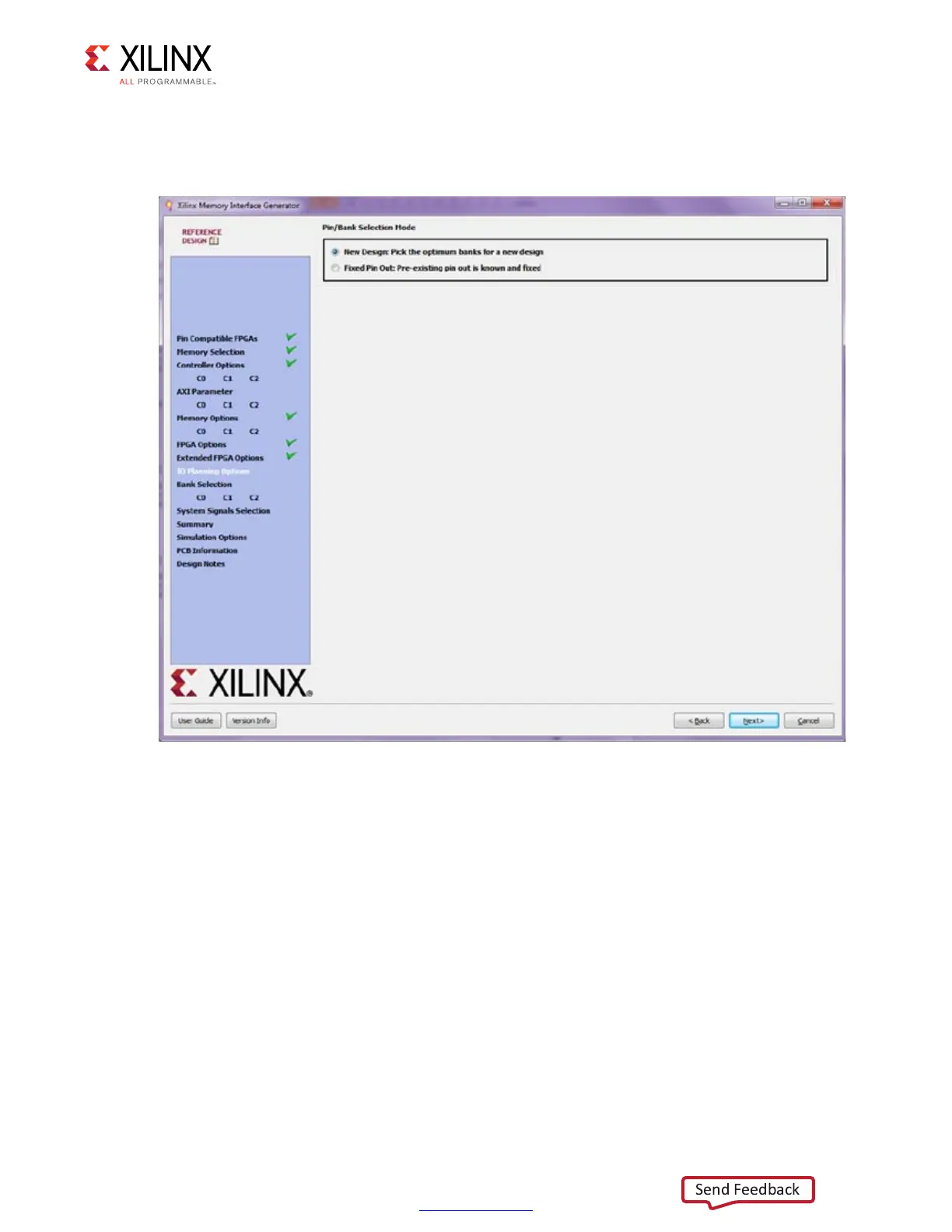

Figure 2-23 shows the I/O Planning Options page.

• Pin/Bank Selection Mode – This allows you to specify an existing pinout and generate

the RTL for this pinout or pick banks for a new design. Figure 2-24 shows the options

for using an existing pinout. You must assign the appropriate pins for each signal. A

choice of each bank is available to narrow down the list of pins. It is not mandatory to

select the banks prior to selection of the pins. Click Validate to check against the MIG

pinout rules. You cannot proceed until the MIG DRC has been validated by clicking

Validate.

X-Ref Target - Figure 2-23

Figure 2-23: I/O Planning Options Page

Loading...

Loading...