Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 296

UG586 November 30, 2016

www.xilinx.com

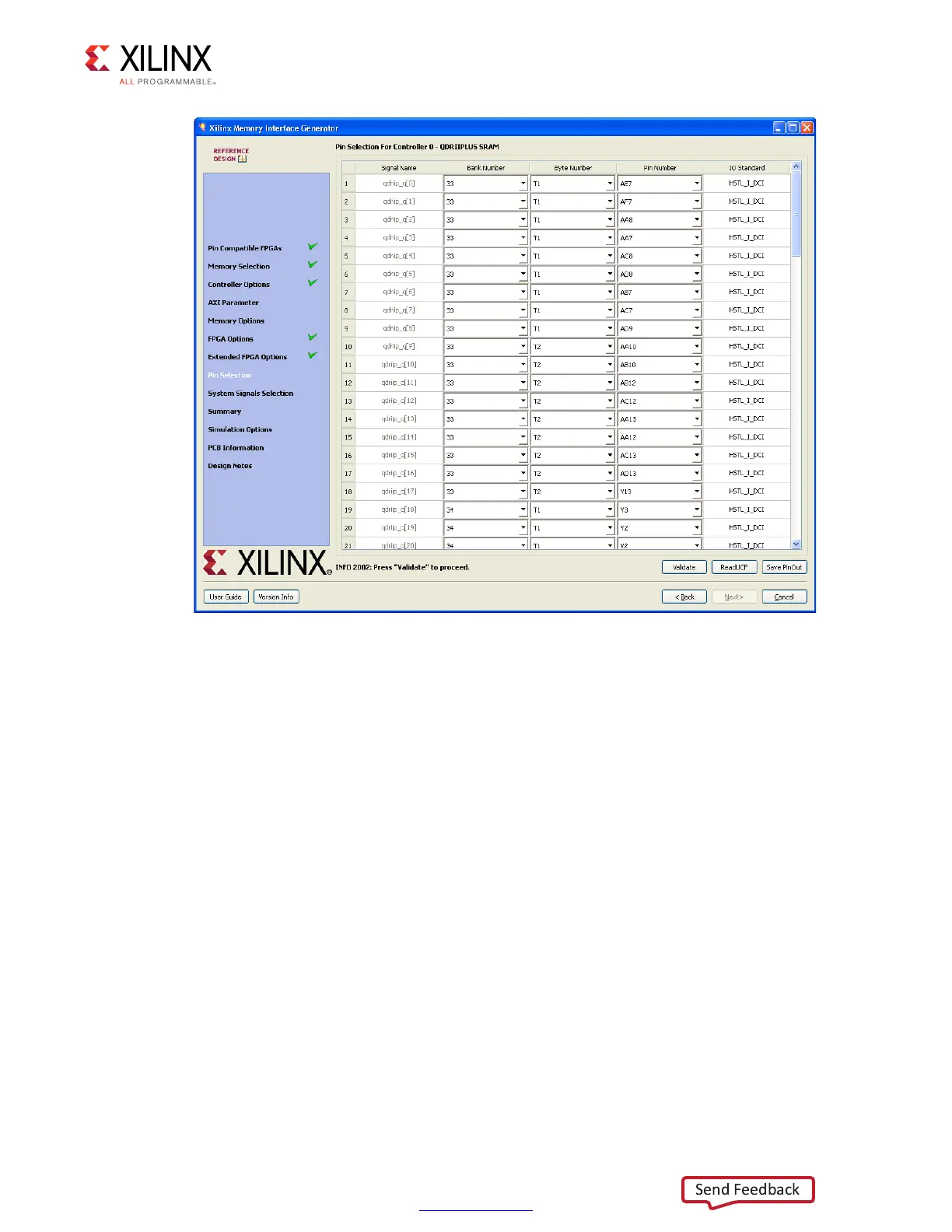

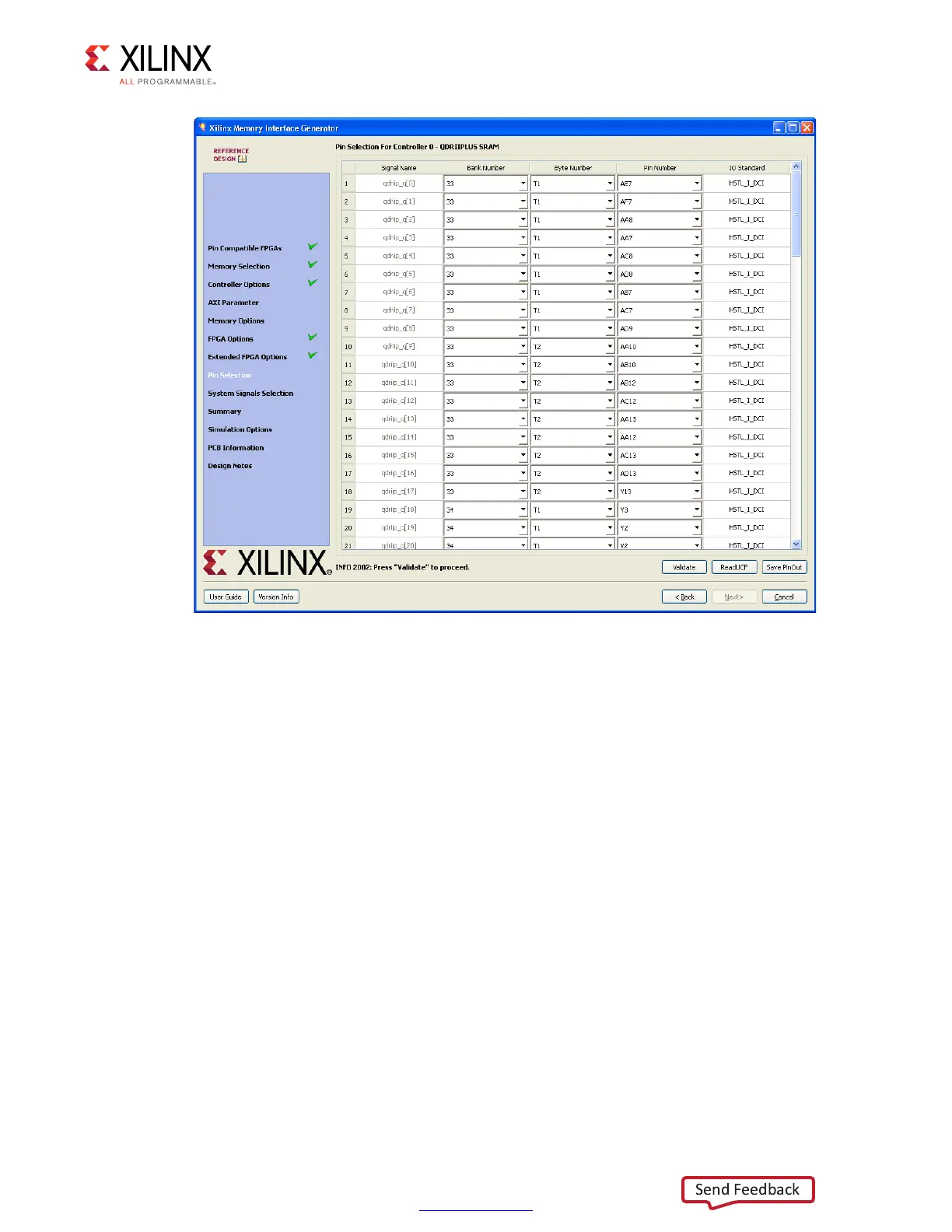

Chapter 2: QDR II+ Memory Interface Solution

Bank Selection

This feature allows the selection of bytes for the memory interface. Bytes can be selected

for different classes of memory signals, such as:

• Address and control signals

• Data Read signals

• Data Write signals

For customized settings, click Deselect Banks and select the appropriate bank and memory

signals. Click Next to move to the next page if the default setting is used. To unselect the

banks that are selected, click Deselect Banks. To restore the defaults, click Restore

Defaults. VCCAUX_IO groups are shown for HP banks in devices with these groups using

dashed lines. VCCAUX_IO is common to all banks in these groups. The memory interface

must have the same VCCAUX_IO for all banks used in the interface. MIG automatically sets

the VCCAUX_IO constraint appropriately for the data rate requested.

For devices implemented with SSI technology, the SLRs are indicated by a number in the

header in each bank, for example, SLR 1. Interfaces cannot span across Super Logic Regions.

Not all devices have Super Logic Regions.

X-Ref Target - Figure 2-24

Figure 2-24: Pin/Bank Selection Mode

Loading...

Loading...