Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 104

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

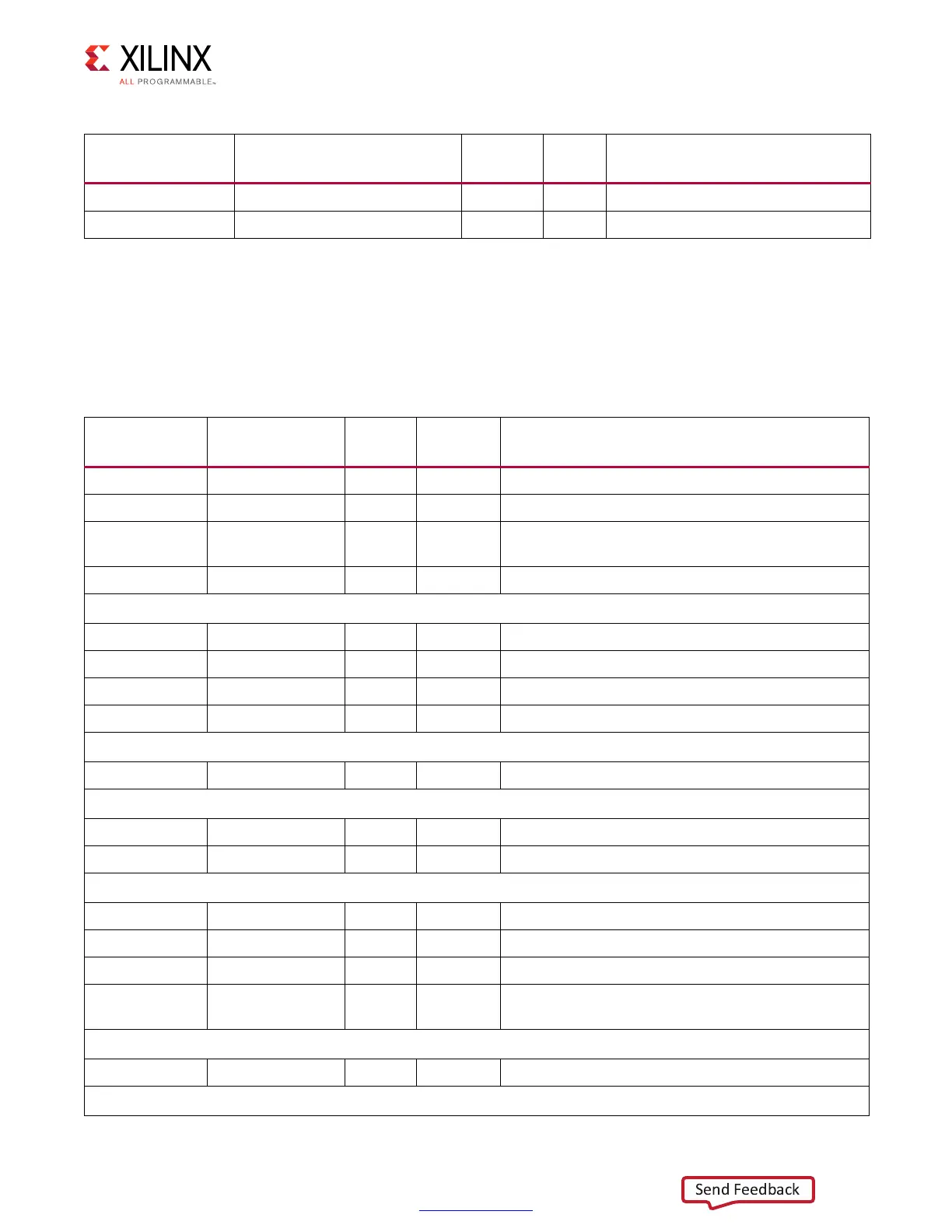

AXI4-Lite Slave Control/Status Register Map

ECC register map is shown in Table 1-23. The register map is Little Endian. Write accesses to

read-only or reserved values are ignored. Read accesses to write-only or reserved values

return the value 0xDEADDEAD.

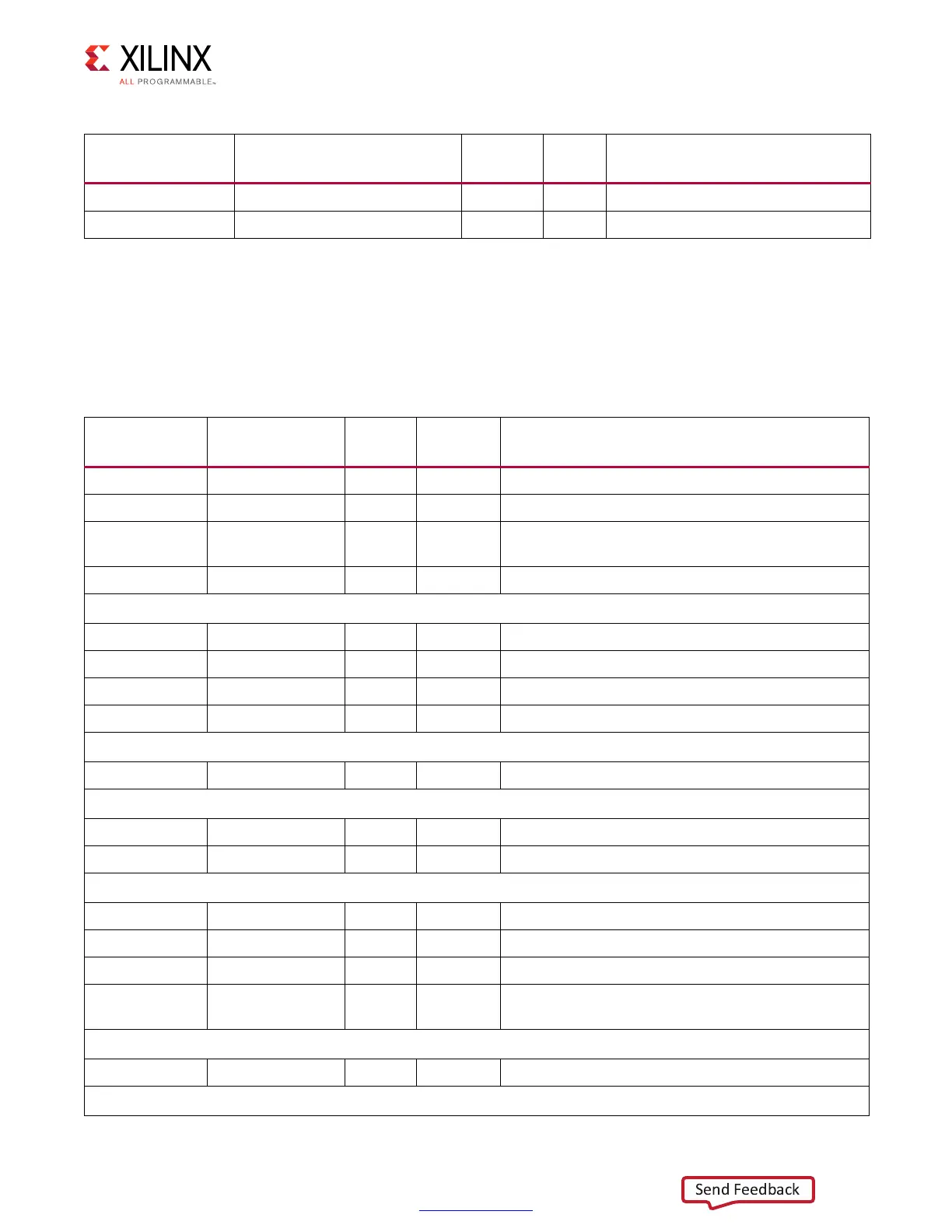

s_axi_ctrl_rready 1 Input Read ready.

interrupt 1 Output High IP Global Interrupt signal

Table 1-22: List of New I/O Signals (Cont’d)

Name Width Direction

Active

State

Description

Table 1-23: ECC Control Register Map

Address Offset Register Name

Access

Type

Default

Value

Description

0x00 ECC_STATUS R/W 0x0 ECC Status Register

0x04 ECC_EN_IRQ R/W 0x0 ECC Enable Interrupt Register

0x08 ECC_ON_OFF R/W

0x0 or

0x1

ECC On/Off Register. If C_ECC_ONOFF_RESET_

VALUE = 1, the default value is 0x1.

0x0C CE_CNT R/W 0x0 Correctable Error Count Register

(0x10–0x9C) Reserved

0x100 CE_FFD[31:00] R 0x0 Correctable Error First Failing Data Register.

0x104 CE_FFD[63:32] R 0x0 Correctable Error First Failing Data Register

0x108 CE_FFD[95:64]

(1)

R 0x0 Correctable Error First Failing Data Register.

0x10C CE_FFD [127:96]

(1)

R 0x0 Correctable Error First Failing Data Register.

(0x110–0x17C) Reserved

0x180 CE_FFE R 0x0 Correctable Error First Failing ECC Register.

(0x184–0x1BC) Reserved

0x1C0 CE_FFA[31:0] R 0x0 Correctable Error First Failing Address

0x1C4 CE_FFA[63:32]

(2)

R 0x0 Correctable Error First Failing Address

(0x1C8–0x1FC) Reserved

0x200 UE_FFD [31:00] R 0x0 Uncorrectable Error First Failing Data Register

0x204 UE_FFD [63:32] R 0x0 Uncorrectable Error First Failing Data Register

0x208 UE_FFD [95:64]

(1)

R 0x0 Uncorrectable Error First Failing Data Register

0x20C

UE_FFD

[127:96]

(1)

R 0x0 Uncorrectable Error First Failing Data Register

(0x210–0x27C) Reserved

0x280 UE_FFE R 0x0 Uncorrectable Error First Failing ECC Register

(0x284–0x2BC) Reserved

Loading...

Loading...