Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 249

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Debugging MPR Read Leveling Failures – DDR3 Only (dbg_rdlvl_err[1] = 1)

Calibration Overview

At this stage of calibration, the write DQS is not centered in the write DQ window, nor is the

read DQS centered in the read DQ window. The DDR3 Multi-Purpose Register (MPR) is used

to center the read DQS in the read DQ window. The MPR has a pre-defined “01010101” or

“10101010” pattern that is read back during this stage of calibration. The read DQS

centering is required for the next stage of calibration, OCLKDELAYED calibration.

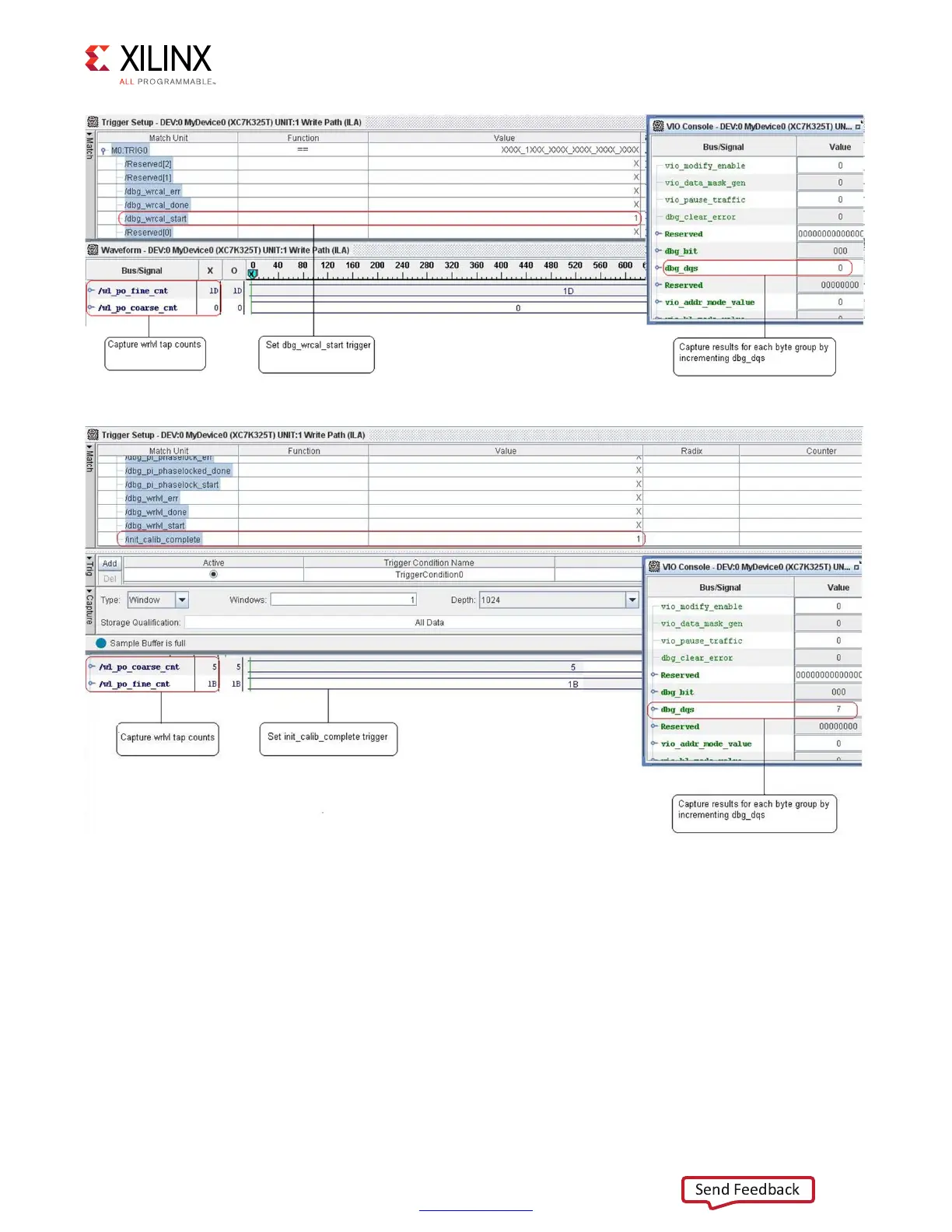

X-Ref Target - Figure 1-100

Figure 1-100: Trigger = dbg_wrcal_start

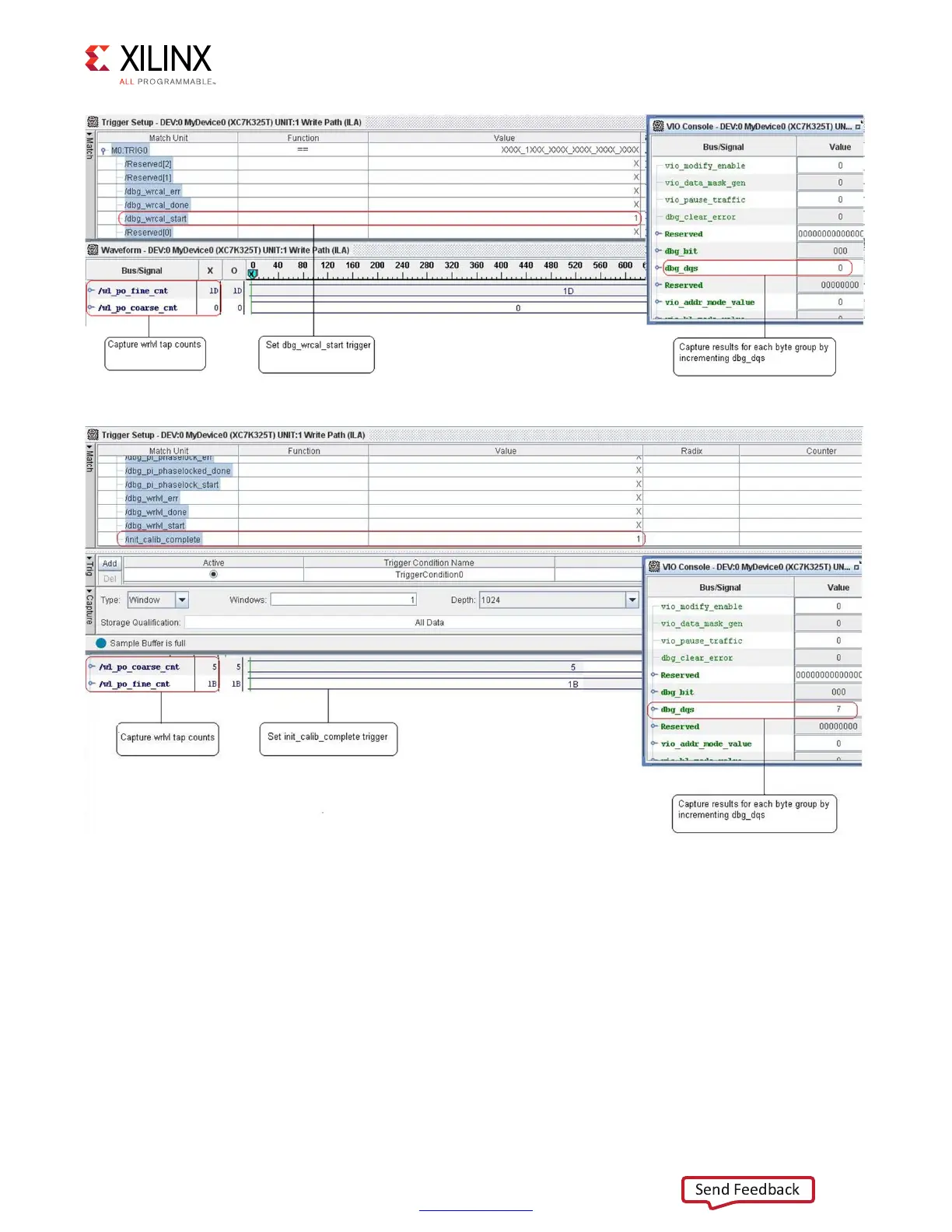

X-Ref Target - Figure 1-101

Figure 1-101: Trigger = init_calib_complete

Loading...

Loading...