Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 47

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Memory Model License

The MIG tool can output a chosen vendor’s memory model for simulation purposes for

memories such as DDR2 or DDR3 SDRAMs. To access the models in the output sim folder,

click the license agreement (Figure 1-28). Read the license agreement and check the Accept

License Agreement box to accept it. If the license agreement is not agreed to, the memory

model is not made available. A memory model is necessary to simulate the design.

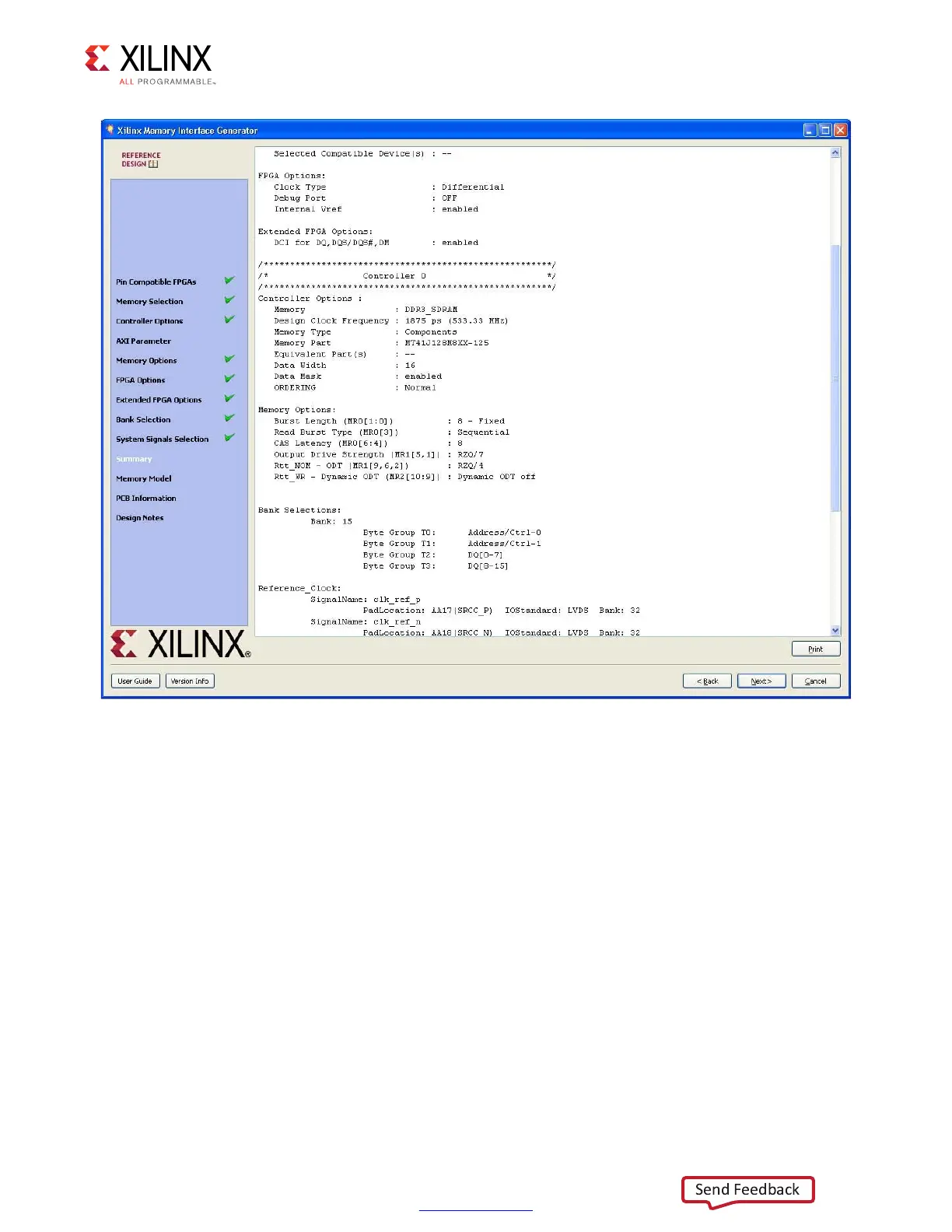

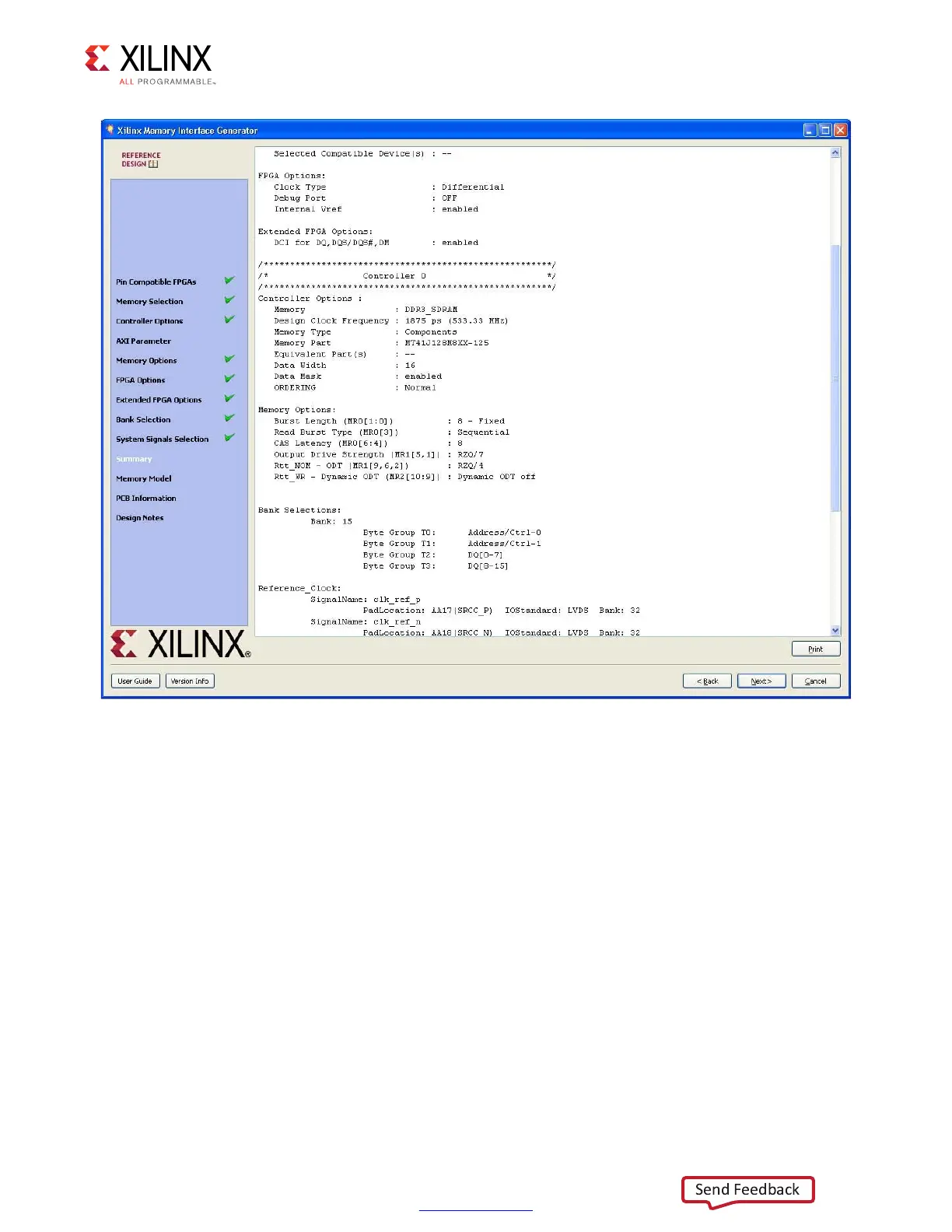

X-Ref Target - Figure 1-27

Figure 1-27: Summary

Loading...

Loading...