Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 440

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

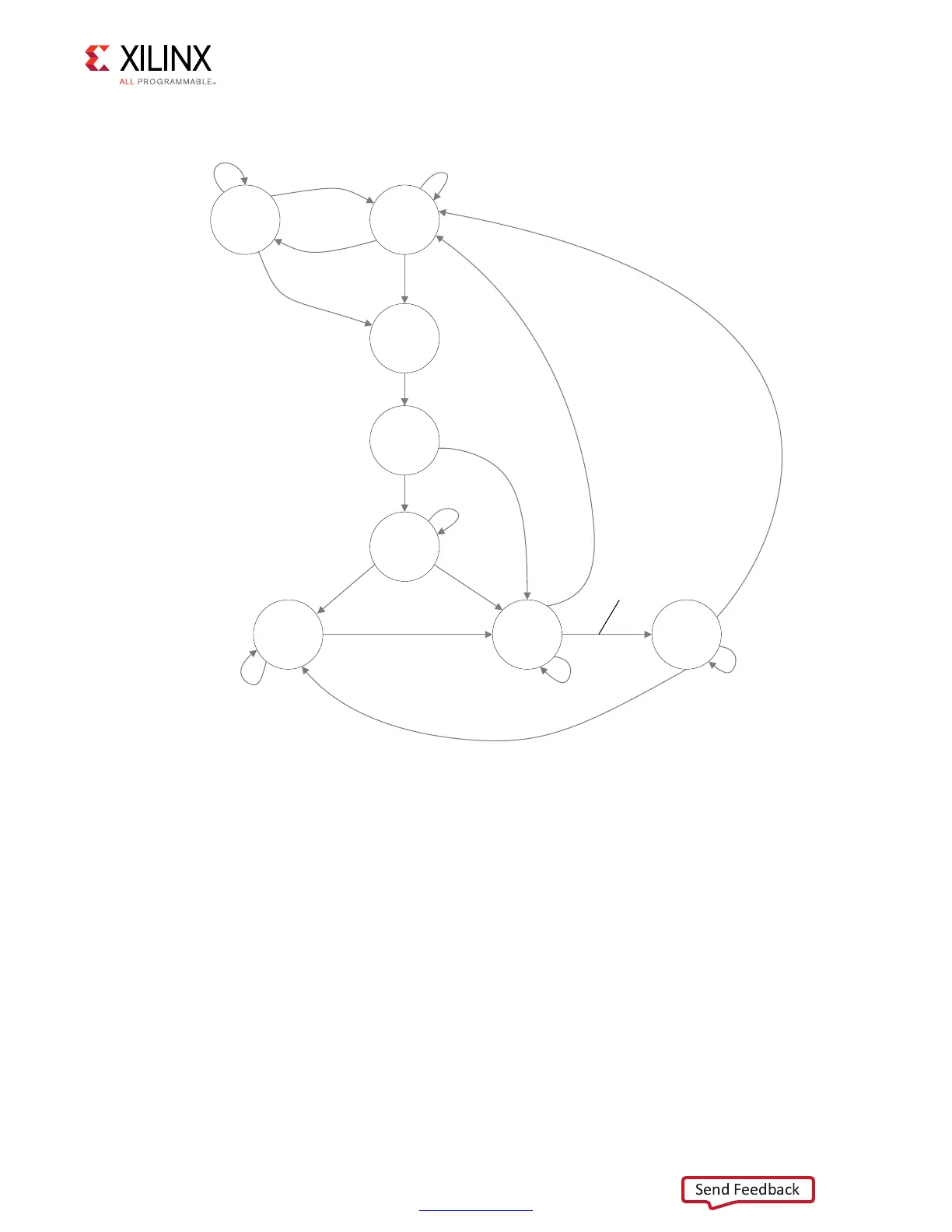

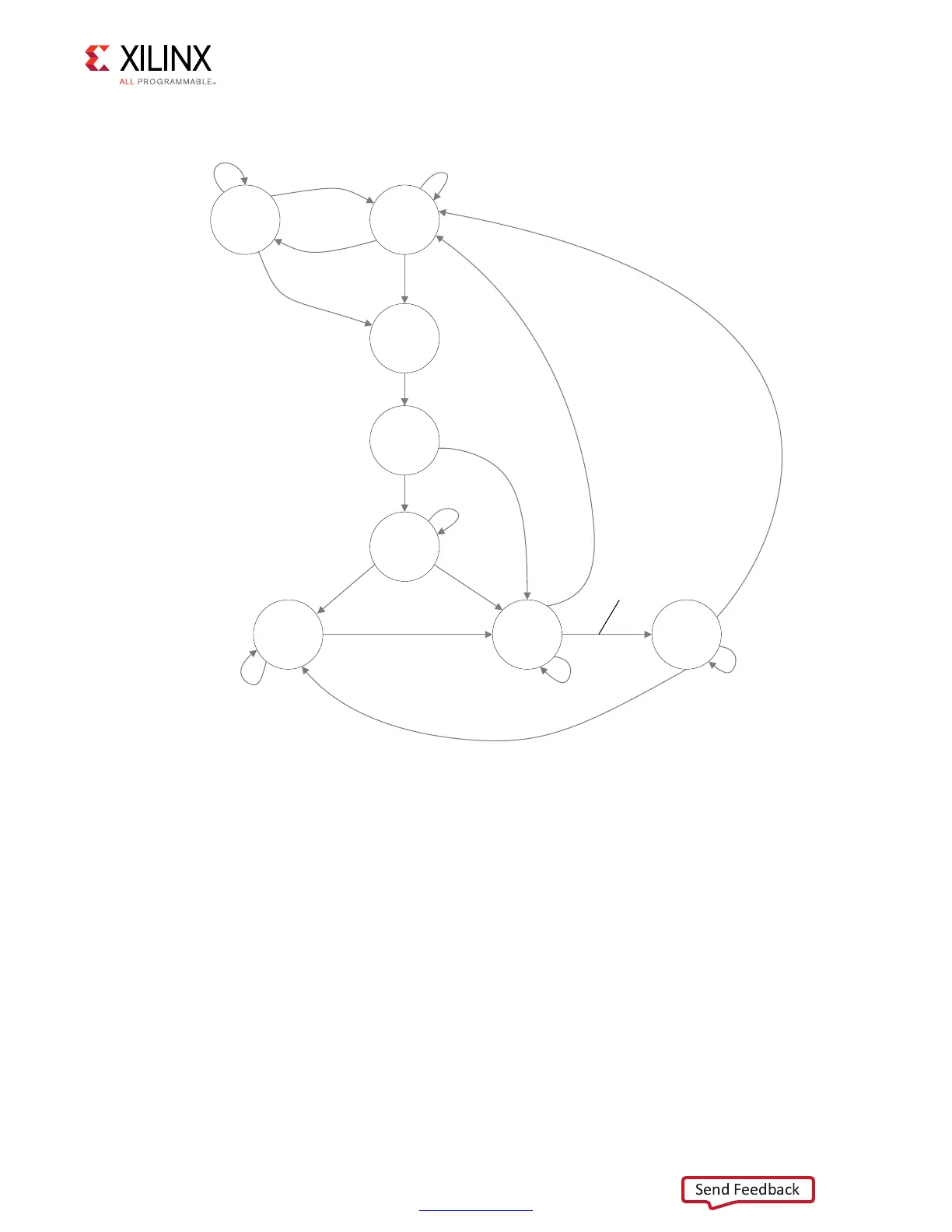

Figure 3-47 shows the state machine logic for the controller.

PHY Architecture

The PHY consists of dedicated blocks and soft calibration logic. The dedicated blocks are

structured adjacent to one another with back-to-back interconnects to minimize the clock

and datapath routing necessary to build high-performance physical layers.

Some of the dedicated blocks that are used in the RLDRAM II/RLDRAM 3 PHY and their

features are described as follows:

• I/Os available within each FPGA bank are grouped into four byte groups, where each

byte group consists of up to 12 I/Os.

X-Ref Target - Figure 3-47

Figure 3-47: Controller State Machine Logic (CMD_PER_CLK == 1 or 2)

#4,?)$,%

#4,?,/!

$?#-$

#4,?,/!

$?#-$

#4,?02

/#?,!3

4?#-$

#4,?02

/#?#-$

/2

CAL?DONE

#4,?02

/#?2%&2

#4,?02

/#?,!3

4?#-$

#4,?02

/#?#-$

REFR?REQ

CMD?EMPTY

REFR?DONE

CMD?EMPTY

REFR?DONE

CMD?EMPTY

REFR?DONE

CMD?EMPTY

CMD?EMPTY

RD?GRANT;=\\

WR?GRANT;=

BANKS?MATCH?R;=

\\WR?TO?RD?R

RD?GRANT;=\\

WR?GRANT;=

CMD?EMPTY\\

REFR?REQ

RD?GRANT;=\\WR?GRANT;=

BANKS?MATCH?R;=WR?TO?RD?R

RD?GRANT;=WR?GRANT;=

#-$?0%2?#,+

NOP?REQ;=RD?GRANT;=

WR?GRANT;=NOP?REQ;=

/2

RD?GRANT;=\\WR?GRANT;=

BANKS?MATCH?R;=\\

WR?TO?RD?R

RD?GRANT;=WR?GRANT;=

#-$?0%2?#,+

NOP?REQ;=RD?GRANT;=

WR?GRANT;=NOP?REQ;=

RD?GRANT;=\\WR?GRANT;=\\

NOP?REQ;=

RD?GRANT;=\\WR?GRANT;=

CMD?EMPTY

REFR?REQ

RD?GRANT;=\\WR?GRANT;=

CMD?EMPTY\\REFR?REQ

RD?GRANT;=

WR?GRANT;=

RD?GRANT;=

WR?GRANT;=

NOP?REQ;=

RD?GRANT;=

WR?GRANT;=

#-$?0%2?#,

+\\

NOP?REQ;=

8

Loading...

Loading...