Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 317

UG586 November 30, 2016

www.xilinx.com

Chapter 2: QDR II+ Memory Interface Solution

Core Architecture

Overview

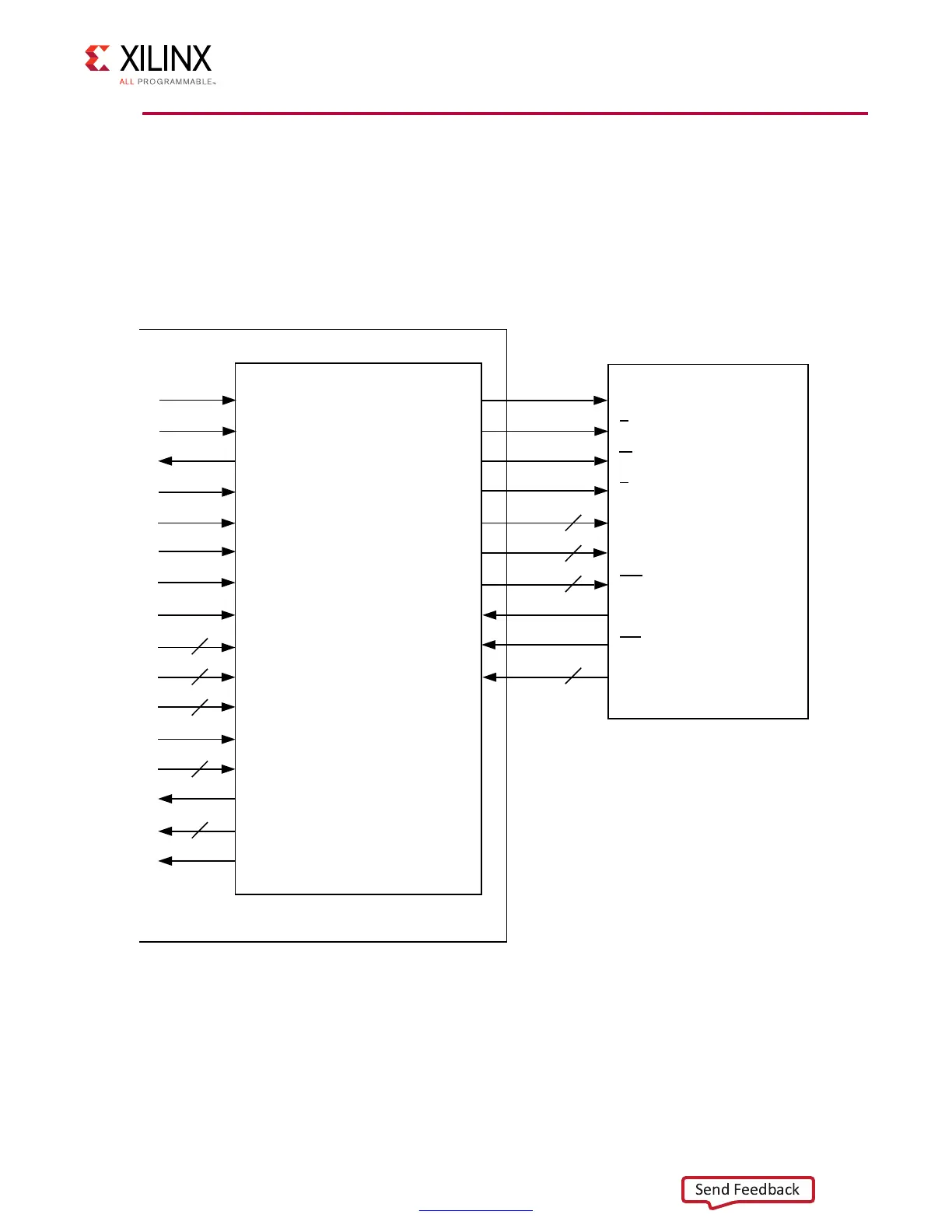

Figure 2-38 shows a high-level block diagram of the 7 series FPGA QDR II+ SRAM interface

solution. This figure shows both the internal FPGA connections to the client interface for

initiating read and write commands, and the external interface to the memory device.

X-Ref Target - Figure 2-38

Figure 2-38: High-Level Block Diagram of QDR II+ Interface Solution

8*BFBB

4'5,,65$0

.

.

:

5

6$

'

%:

4

3K\VLFDO

,QWHUIDFH

&OLHQW

,QWHUIDFH

TGUBEZBQ

TGUBFTBS

TGUBFTBQ

TGUBT

FON

V\VBUVW

UVWBGN

FONBZU

FONBPHP

PPFPBORFNHG

LRGHOD\BFWUOBUG\

&4

6HULHV)3*$

&4

TGUBNBS

TGUBNBQ

TGUBZBQ

TGUBUBQ

TGUBVD

TGUBG

DSSBZUBFPG

DSSBZUBDGGU

DSSBZUBGDWD

DSSBZUBEZBQ

DSSBUGBFPG

DSSBUGBDGGU

DSSBUGBYDOLG

DSSBUGBGDWD

LQLWBFDOLEBFRPSOHWH

Loading...

Loading...