Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 389

UG586 November 30, 2016

www.xilinx.com

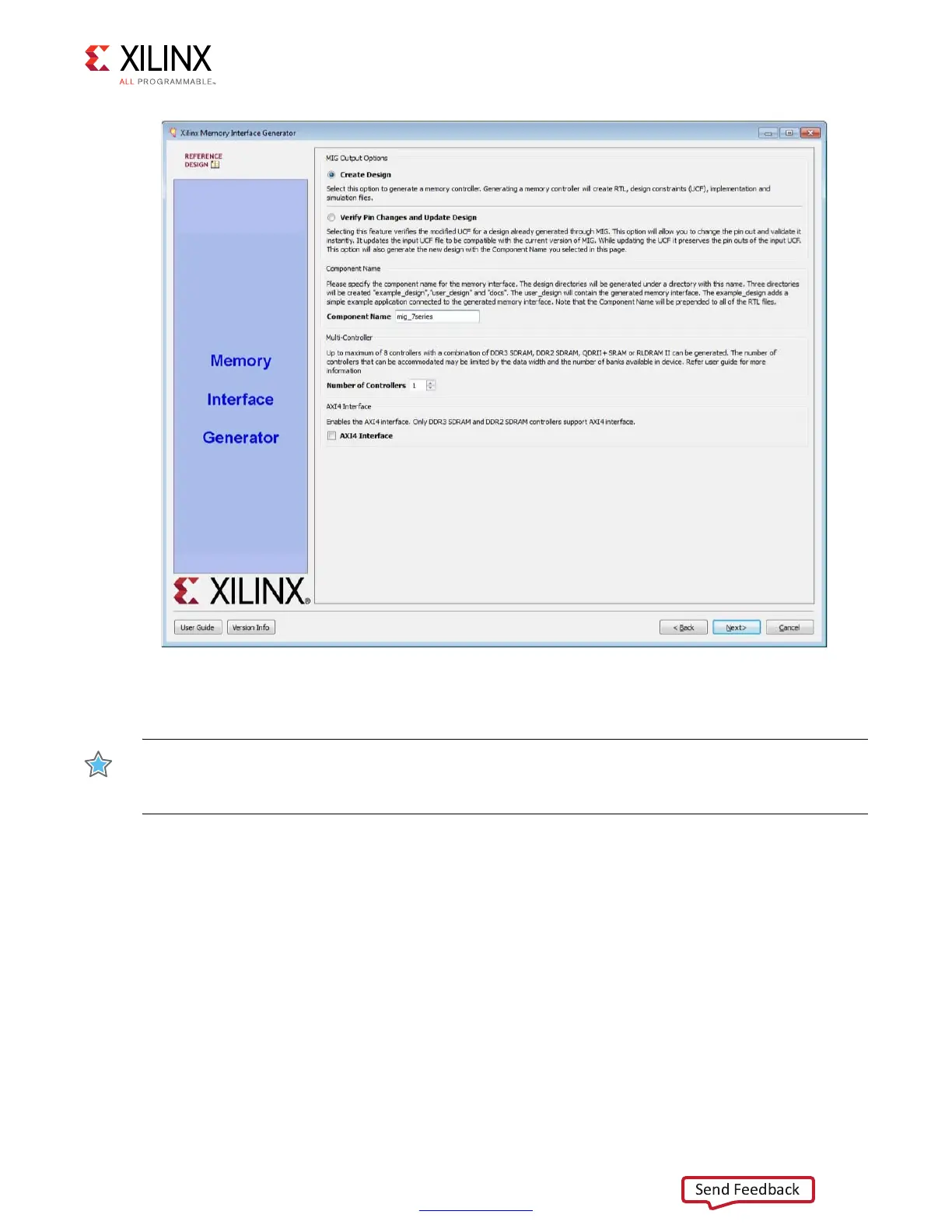

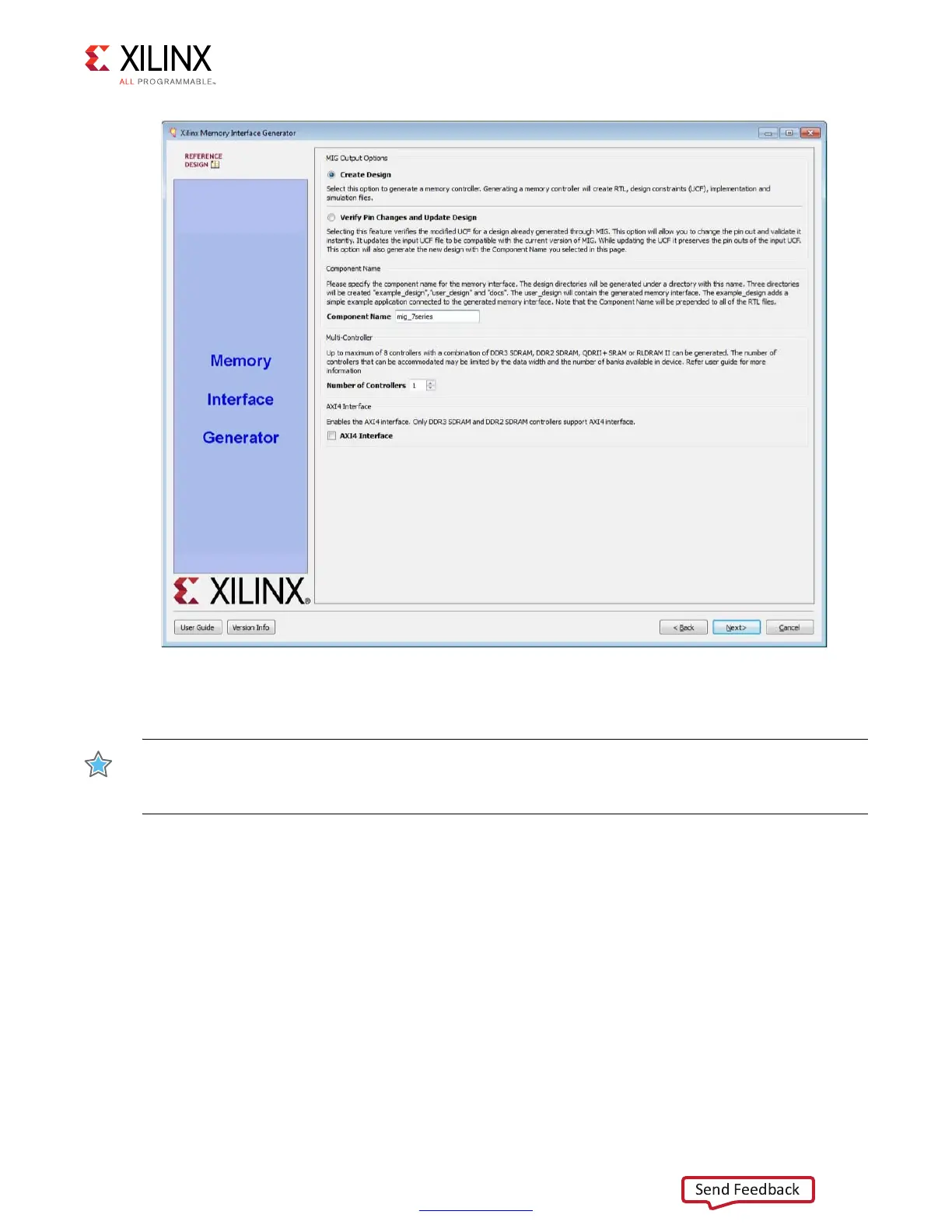

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

MIG outputs are generated with the folder name <component name>.

IMPORTANT: Only alphanumeric characters can be used for <component name>. Special characters

cannot be used. This name should always start with an alphabetical character and can end with an

alphanumeric character.

When invoked from Xilinx Platform Studio (XPS), the component name is corrected to be

the IP instance name from XPS.

3. Click Next to display the Pin Compatible FPGAs page.

Pin Compatible FPGAs

The Pin Compatible FPGAs page lists FPGAs in the selected family having the same

package. If the generated pinout from the MIG tool needs to be compatible with any of

these other FPGAs, this option should be used to select the FPGAs with which the pinout

has to be compatible (Figure 3-15).

X-Ref Target - Figure 3-14

Figure 3-14: MIG Output Options

Loading...

Loading...