Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 658

UG586 November 30, 2016

www.xilinx.com

Chapter 5: Multicontroller Design

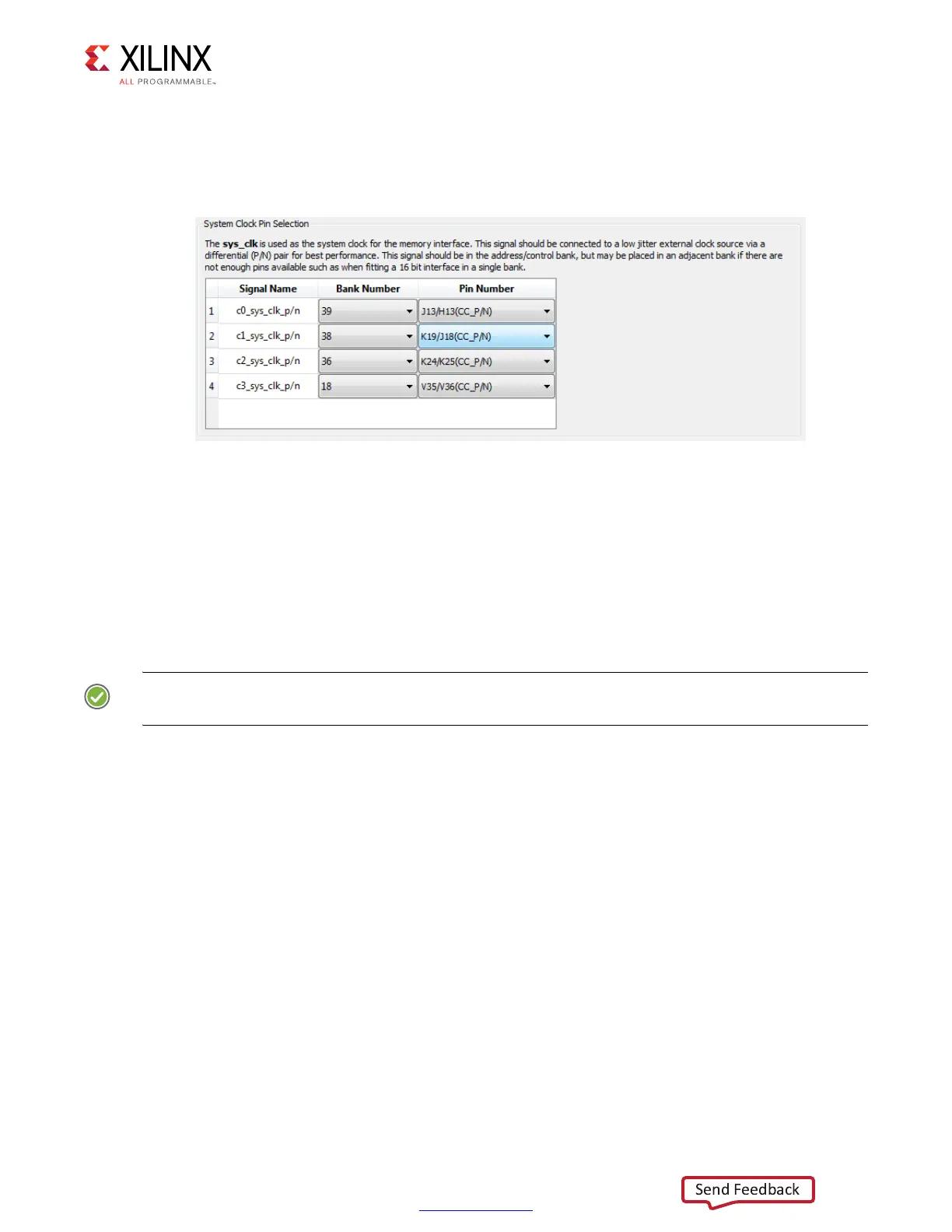

System Clock Pins Selection

Select the system clock pins on the System Pins Selection page. System clock pins can be

selected for each controller; this varies based on the number of controllers (Figure 5-18).

System Clock Sharing

The criteria for sharing a system clock pin is as follows:

• System clock pins can be shared across the controllers when the input frequency is the

same for the controllers.

• Pins can be shared across the controllers as long as the memory interface chosen banks

are in the same column.

RECOMMENDED: Although the MIG allows system clock selection to be in different super logic regions

(SLRs), it is not recommended due to the additional clock jitter in this topology.

• One CCIO port can drive any number of PLLs and there is no restriction on maximum

number of PLLs that a system clock pin can drive. So the same pin can be used for any

number of controllers.

• MIG validates the rules after clicking Next and following the selection for System Clock

pins is done.

• Selecting the same pin indicates the same pin is shared across the controllers.

• One PLL and one MMCM are needed for each controller regardless of system clock pin

is shared or not. System clock pin can only be shared and no other resources (PLL or

MMCM) are shared across controllers.

X-Ref Target - Figure 5-18

Figure 5-18: System Clock Pins Selection Page

Loading...

Loading...