Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 66

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Implementing the Example Design

For more information on using an IP example design, see the Vivado Design Suite User

Guide: Designing with IP (UG896) [Ref 7].

Simulating the Example Design (for Designs with the Standard User Interface)

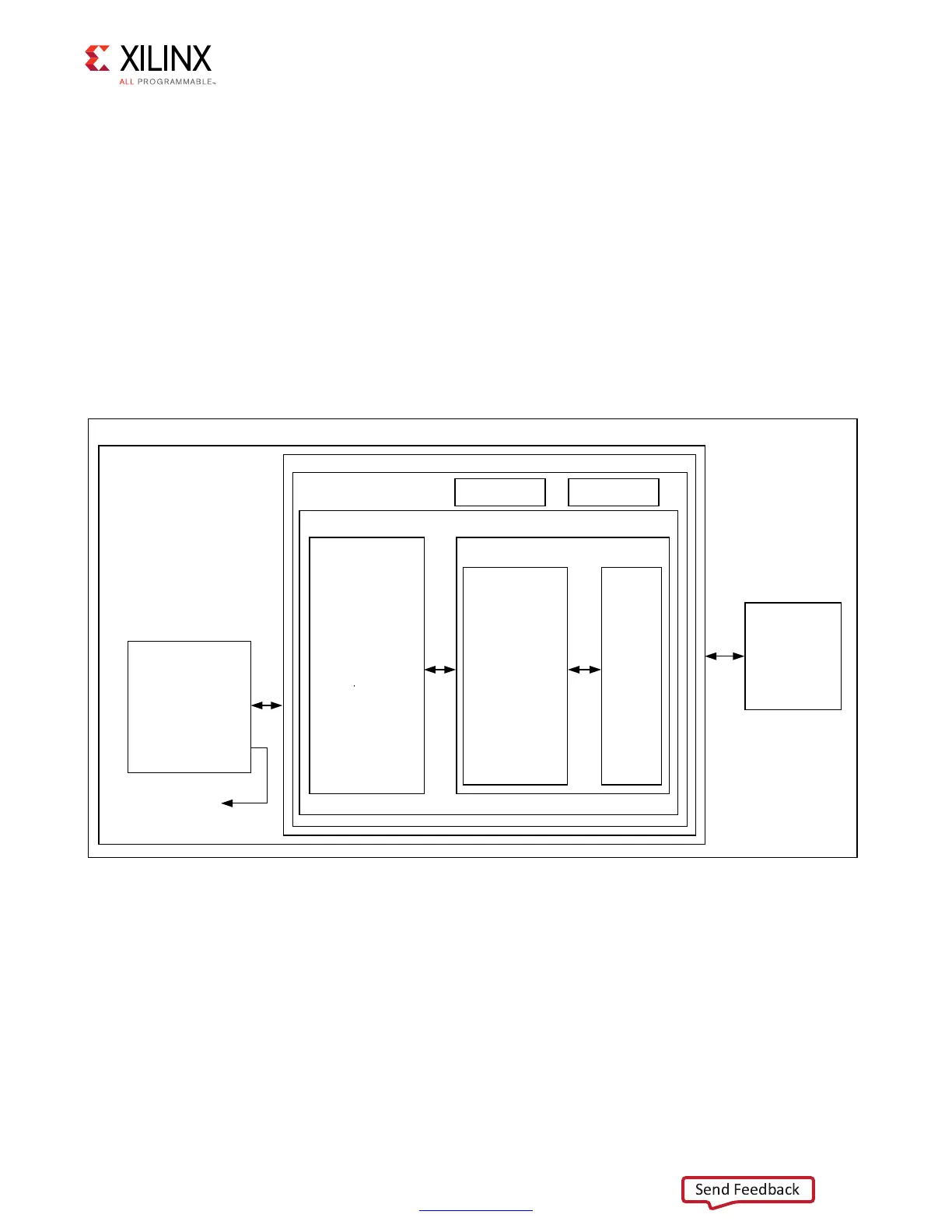

The MIG tool provides a synthesizable test bench to generate various traffic data patterns

to the Memory Controller (MC). This test bench consists of a memc_ui_top wrapper, a

traffic_generator that generates traffic patterns through the user interface to a

ui_top core, and an infrastructure core that provides clock resources to the memc_ui_top

core. A block diagram of the example design test bench is shown in Figure 1-39.

Figure 1-40 shows the simulation result of a simple read and write transaction between the

tb_top and memc_intfc modules.

X-Ref Target - Figure 1-39

Figure 1-39: Synthesizable Example Design Block Diagram

UG586_c1_41_120311

ddr2_sim_tb_top or ddr3_sim_tb_top

Example Design

app_addr

app_cmd

app_en

app_hi_pri

app_wdf_data

app_wdf_end

app_wdf_mask

app_wdf_wren

app_rd_data

app_rd_data_end

app_rd_data_valid

app_wdf_rdy

traffic_gen_top

memc_ui_top

ui_top mem_Intfc

DDR2/DDR3

SDRAM

cmd

accept

use_addr

bank_mach_next

data_buf_addr

wr_data_en

wr_data_addr

wr_data_en

wr_data_be

rd_data_en

rd_data

MC

phy_top

error

Parameter:

BEGIN_ADDR

END_ADDR

nCK_PER_CLK

iodelayctrl infrastructure

app_rdy

user_design_top Wrapper

user_design_top

Loading...

Loading...