Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 320

UG586 November 30, 2016

www.xilinx.com

Chapter 2: QDR II+ Memory Interface Solution

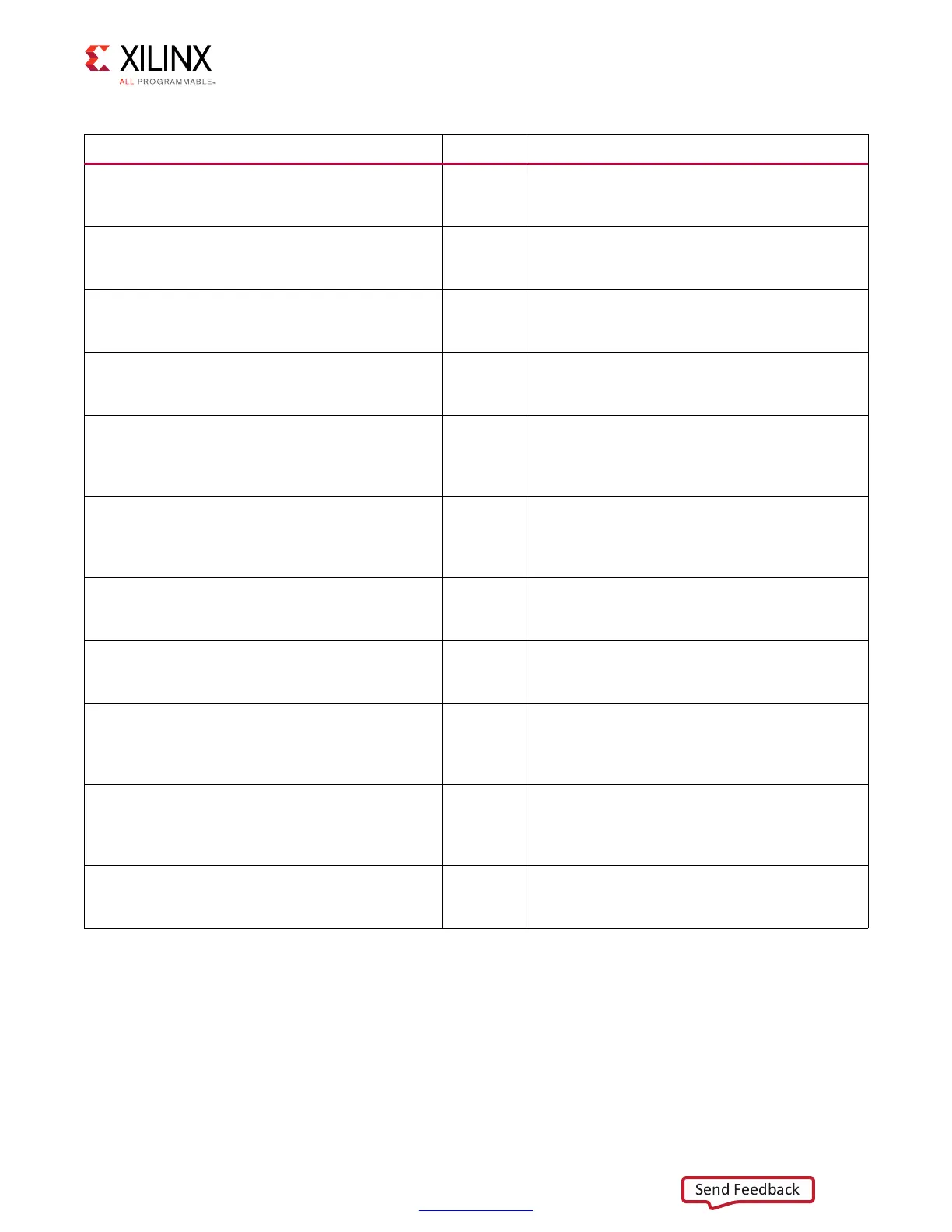

app_rd_cmd1 Input

Read Command. This signal is used to issue a

read request and indicates that the address on

port 1 is valid.

app_rd_data1[DATA_WIDTH × 2 – 1:0] Output

Read Data. This bus carries the data read back

from the read command issued on

app_rd_cmd1.

app_rd_valid1 Output

Read Valid. This signal indicates that data read

back from memory is now available on

app_rd_data1 and should be sampled.

app_wr_addr0[ADDR_WIDTH – 1:0] Input

Write Address. This bus provides the address

for a write request. It is valid when

app_wr_cmd0 is asserted.

app_wr_bw_n0[BW_WIDTH × BURST_LEN – 1:0] Input

Write Byte Writes. This bus provides the byte

writes to use for a write request. It is valid when

app_wr_cmd0 is asserted. These enables are

active-Low.

app_wr_cmd0 Input

Write Command. This signal is used to issue a

write request and indicates that the

corresponding sideband signals on write port 0

are valid.

app_wr_data0[DATA_WIDTH × BURST_LEN – 1:0] Input

Write Data. This bus provides the data to use

for a write request. It is valid when

app_wr_cmd0 is asserted.

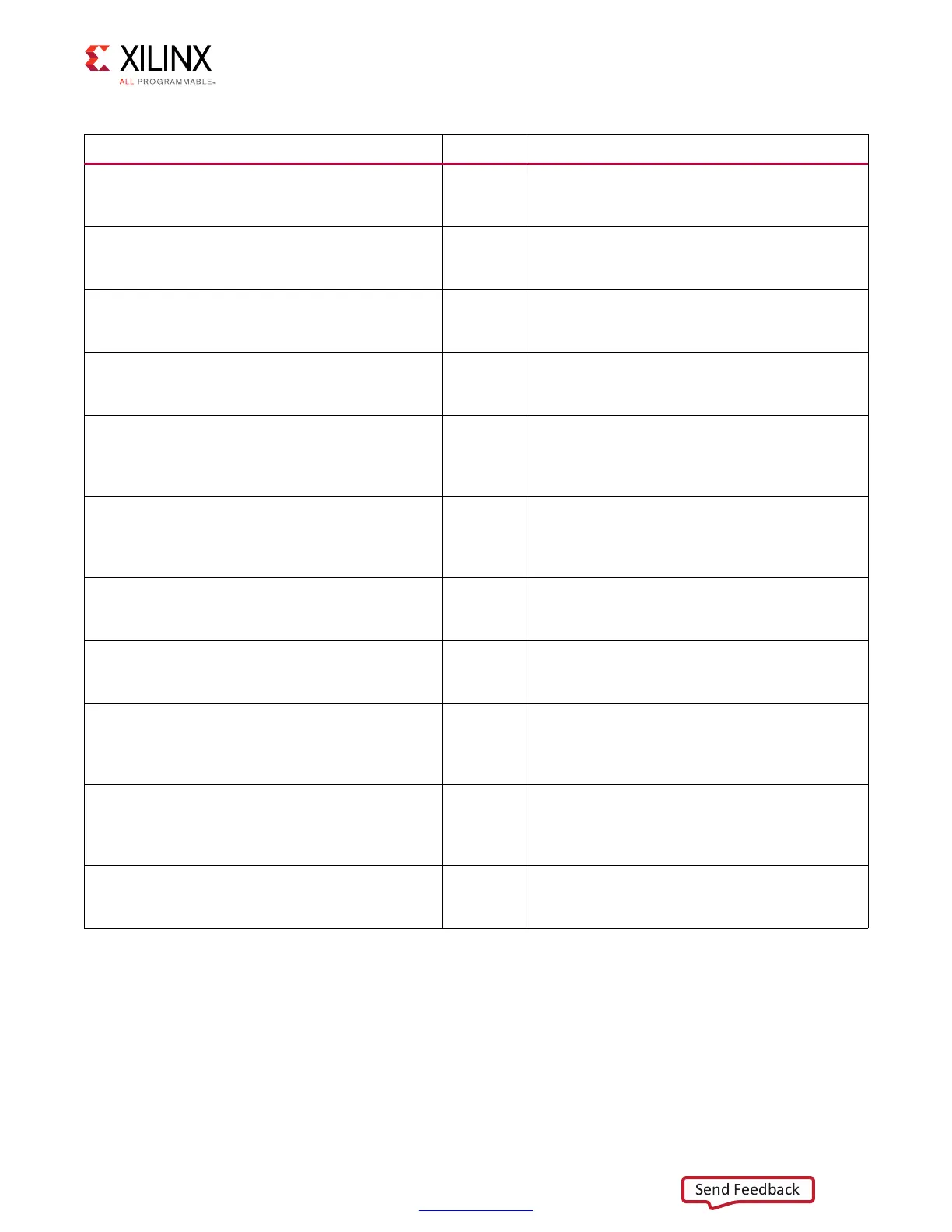

app_wr_addr1[ADDR_WIDTH – 1:0] Input

Write Address. This bus provides the address

for a write request. It is valid when

app_wr_cmd1 is asserted.

app_wr_bw_n1[BW_WIDTH × 2 – 1:0] Input

Write Byte Writes. This bus provides the byte

writes to use for a write request. It is valid when

app_wr_cmd1 is asserted. These enables are

active-Low.

app_wr_cmd1 Input

Write Command. This signal is used to issue a

write request and indicates that the

corresponding sideband signals on write port 1

are valid.

app_wr_data1[DATA_WIDTH × 2 – 1:0] Input

Write Data. This bus provides the data to use

for a write request. It is valid when

app_wr_cmd1 is asserted.

Table 2-7: Client Interface Request Signals (Cont’d)

Signal Direction Description

Loading...

Loading...