Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 373

UG586 November 30, 2016

www.xilinx.com

Chapter 2: QDR II+ Memory Interface Solution

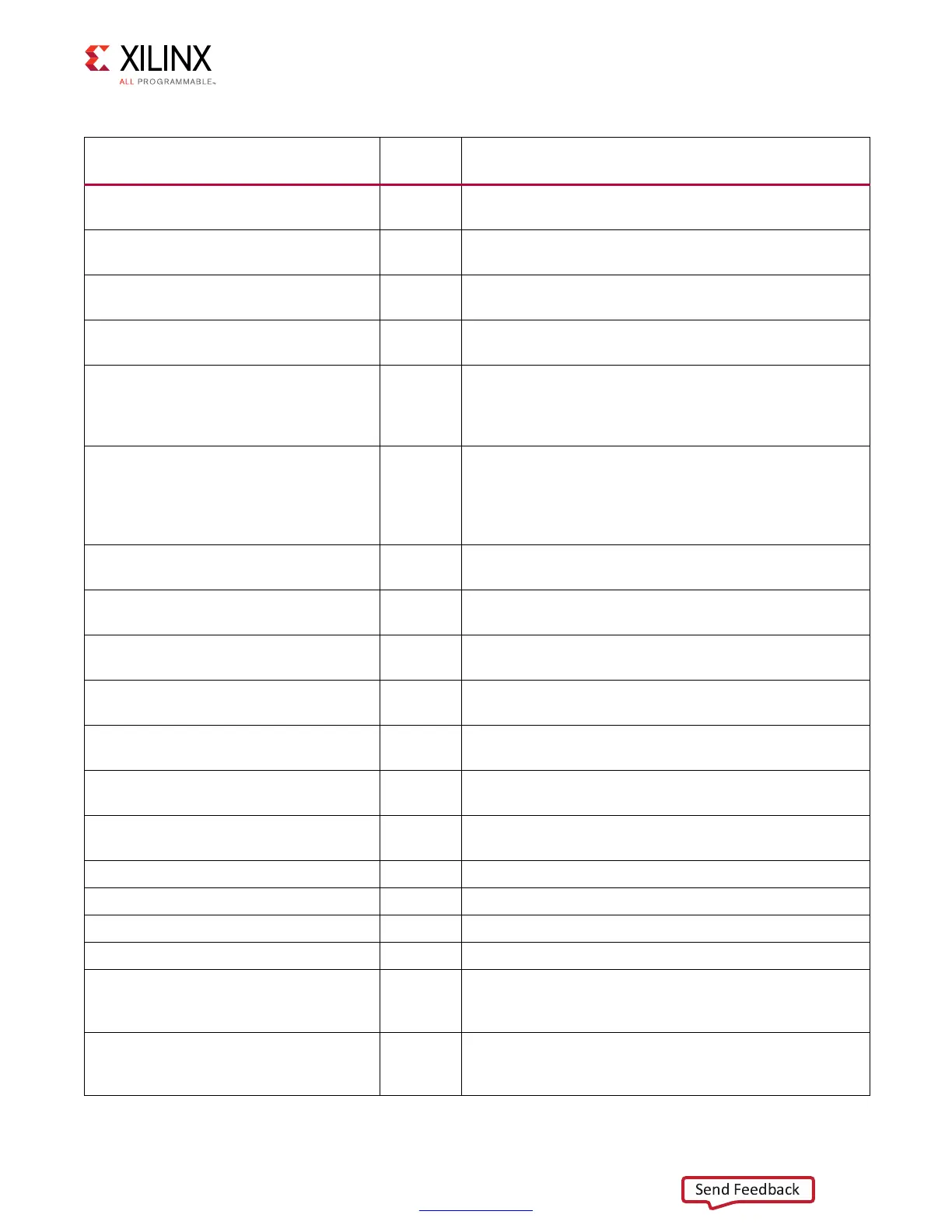

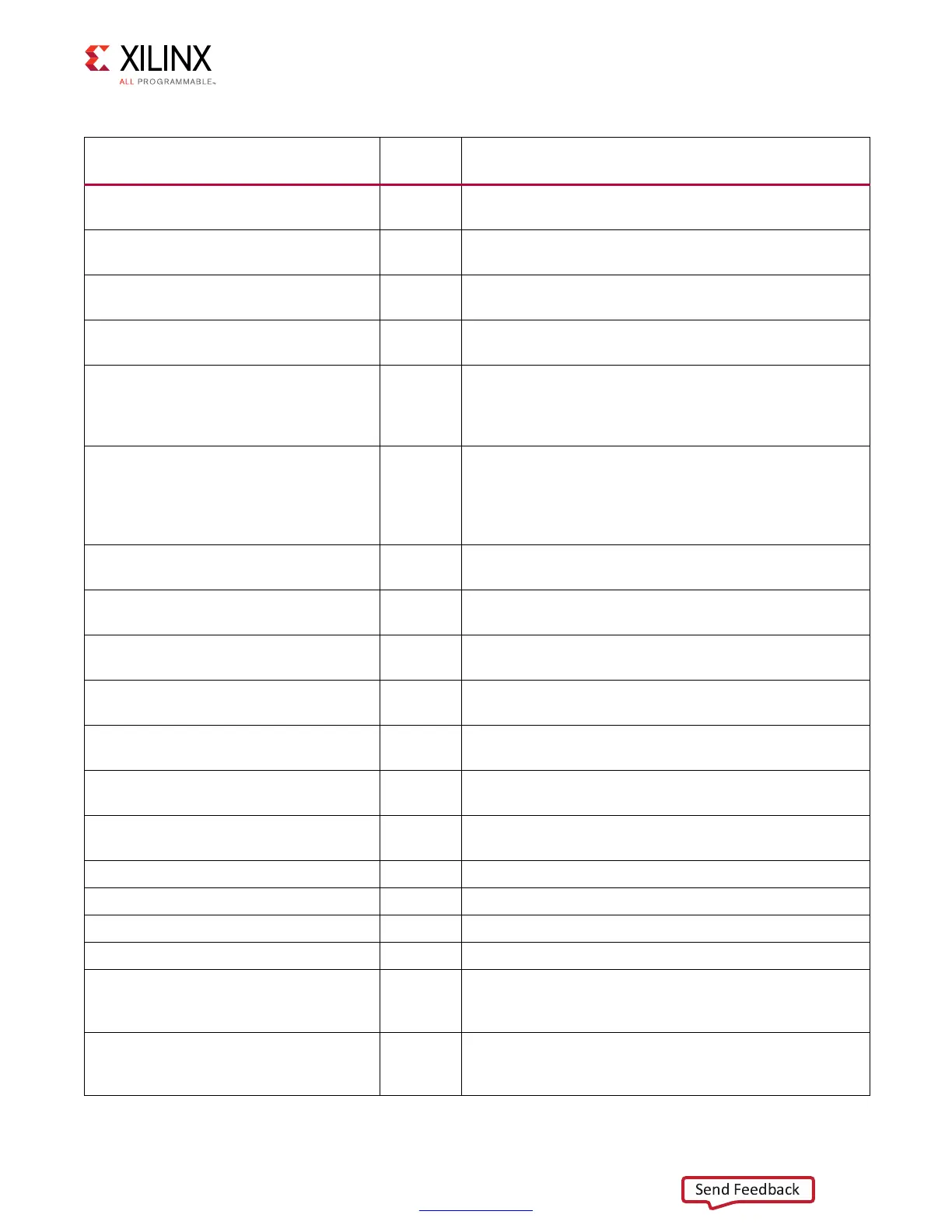

Table 2-18: DEBUG_PORT Signal Descriptions

Signal Direction Description

dbg_phy_wr_cmd_n[1:0] Output

This active-Low signal is the internal wr_cmd used for

debug with the Vivado logic analyzer feature.

dbg_phy_rd_cmd_n[1:0] Output

This active-Low signal is the internal rd_cmd used for

debug with the Vivado logic analyzer feature.

dbg_phy_addr[ADDR_WIDTH × 4 – 1:0] Output

Control address bus used for debug with the Vivado logic

analyzer feature.

dbg_phy_wr_data[DATA_WIDTH × 4 – 1:0] Output

Data being written that is used for debug with the Vivado

logic analyzer feature.

dbg_phy_init_wr_only Input

When this input is High, the state machine in

qdr_phy_write_init_sm stays at the write calibration

pattern to QDR II+ memory. This verifies calibration write

timing. This signal must be Low for normal operation.

dbg_phy_init_rd_only input

When this input is High, the state machine in

qdr_phy_write_init_sm stays at read calibration state from

QDR II+ memory. This verifies calibration read timing and

returned calibration data. This signal must be Low for

normal operation.

dbg_byte_sel Input

This input selects the corresponding byte lane and you set

the phaser/IDELAY tap controls

dbg_pi_f_inc Input

This signal increments the PHASER_IN generated ISERDES

clk that is used to capture rising data

dbg_pi_f_dec Input

This signal decrements the PHASER_IN generated

ISERDES clk that is used to capture rising data

dbg_po_f_inc Input

This signal increments the PHASER_OUT generated

OSERDES clk that is used to capture falling data

dbg_po_f_dec Input

This signal increments the PHASER_OUT generated

OSERDES clk that is used to capture falling data

dbg_phy_pi_fine_cnt Output

This output indicates the current PHASER_IN tap count

position

dbg_phy_po_fine_cnt Output

This output indicates the current PHASER_OUT tap count

position

dbg_cq_num Output This signal indicates the current CQ/CQ# being calibrated

dbg_q_bit Output This signal indicates the current Q being calibrated

dbg_valid_lat[4:0] Output Latency in cycles of the delayed read command

dbg_q_tapcnt Output Current Q tap setting for each device

dbg_inc_latency Output

This output indicates that the latency of the

corresponding byte lane was increased to ensure proper

alignment of the read data to the user interface.

dbg_error_max_latency Output

This signal indicates that the latency could not be

measured before the counter overflowed. Each device has

one error bit.

Loading...

Loading...