Reference Manual ADuCM356

REGISTER DETAILS: HIGH-SPEED DAC CIRCUITS

analog.com Rev. A | 112 of 312

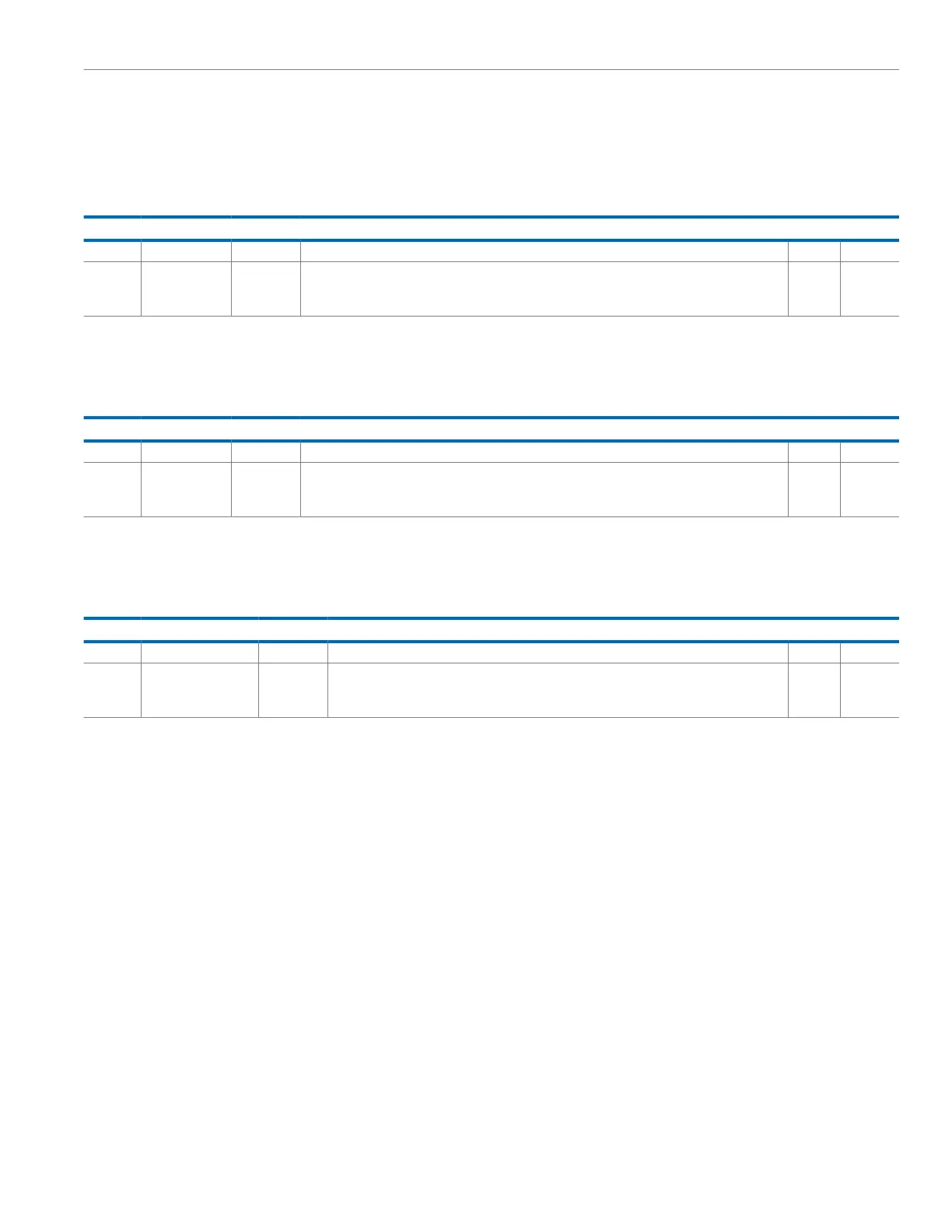

WAVEFORM GENERATOR FOR SINUSOID PHASE OFFSET REGISTER

Address: 0x400C2034, Reset: 0x00000000, Name: WGPHASE

Table 140. Bit Descriptions for WGPHASE

Bits Bit Name Settings Description Reset Access

[31:20] Reserved Reserved. 0x0 R

[19:0] SINEOFFSET Sinusoid Phase Offset. SINOFFSET, Bits[19:0] = phase (degrees)/360 × 2

20

. For example, to achieve

a 45° phase offset, SINOFFSET, Bits[19:0] = 45/360 × 2

20

. This MMR must be set before setting

WGCON, Bits[2:1] and AFECON, Bit 14.

0x0 R/W

WAVEFORM GENERATOR FOR SINUSOID OFFSET REGISTER

Address: 0x400C2038, Reset: 0x00000000, Name: WGOFFSET

Table 141. Bit Descriptions for WGOFFSET

Bits Bit Name Settings Description Reset Access

[31:12] Reserved Reserved. 0x0 R

[11:0] SINEOFFSET Sinusoid Offset. Added to the waveform generator output in sinusoid mode. Signed number

represented in twos complement format. This MMR must be set before setting WGCON, Bits[2:1]

and AFECON, Bit 14.

0x0 R/W

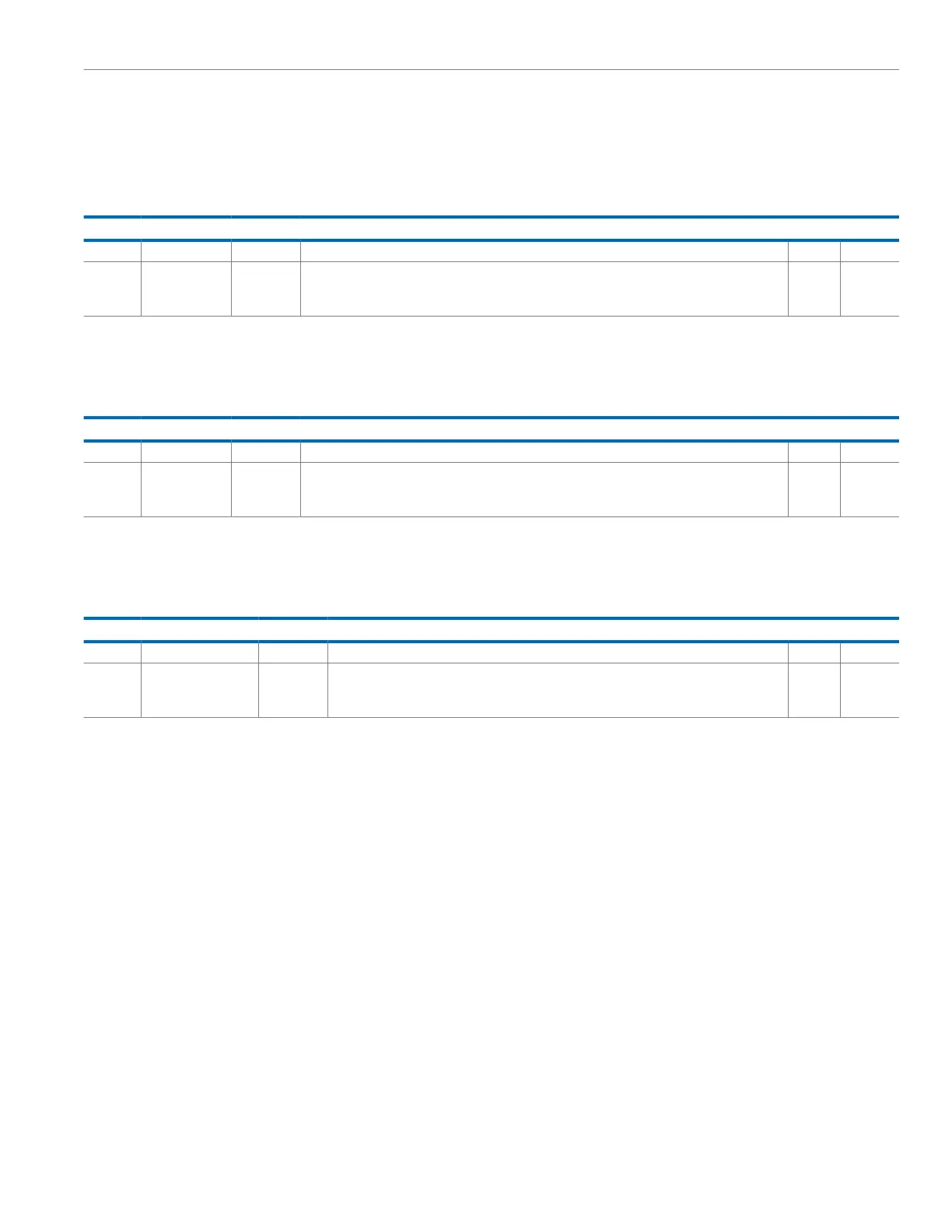

WAVEFORM GENERATOR FOR SINUSOID AMPLITUDE REGISTER

Address: 0x400C203C, Reset: 0x00000000, Name: WGAMPLITUDE

Table 142. Bit Descriptions for WGAMPLITUDE

Bits Bit Name Settings Description Reset Access

[31:11] Reserved Reserved. 0x0 R

[10:0] SINEAMPLITUDE Sinusoid Amplitude. Unsigned number. Scales the waveform generator in sinusoid mode. The

DAC output voltage is determined by the value in HSDACCON, Bit 0 and HSDACCON, Bit 12.

This MMR must be set before setting WGCON, Bits[2:1] and AFECON, Bit 14.

0x0 R/W

Loading...

Loading...