Reference Manual ADuCM356

REGISTER DETAILS: ADC CIRCUIT

analog.com Rev. A | 67 of 312

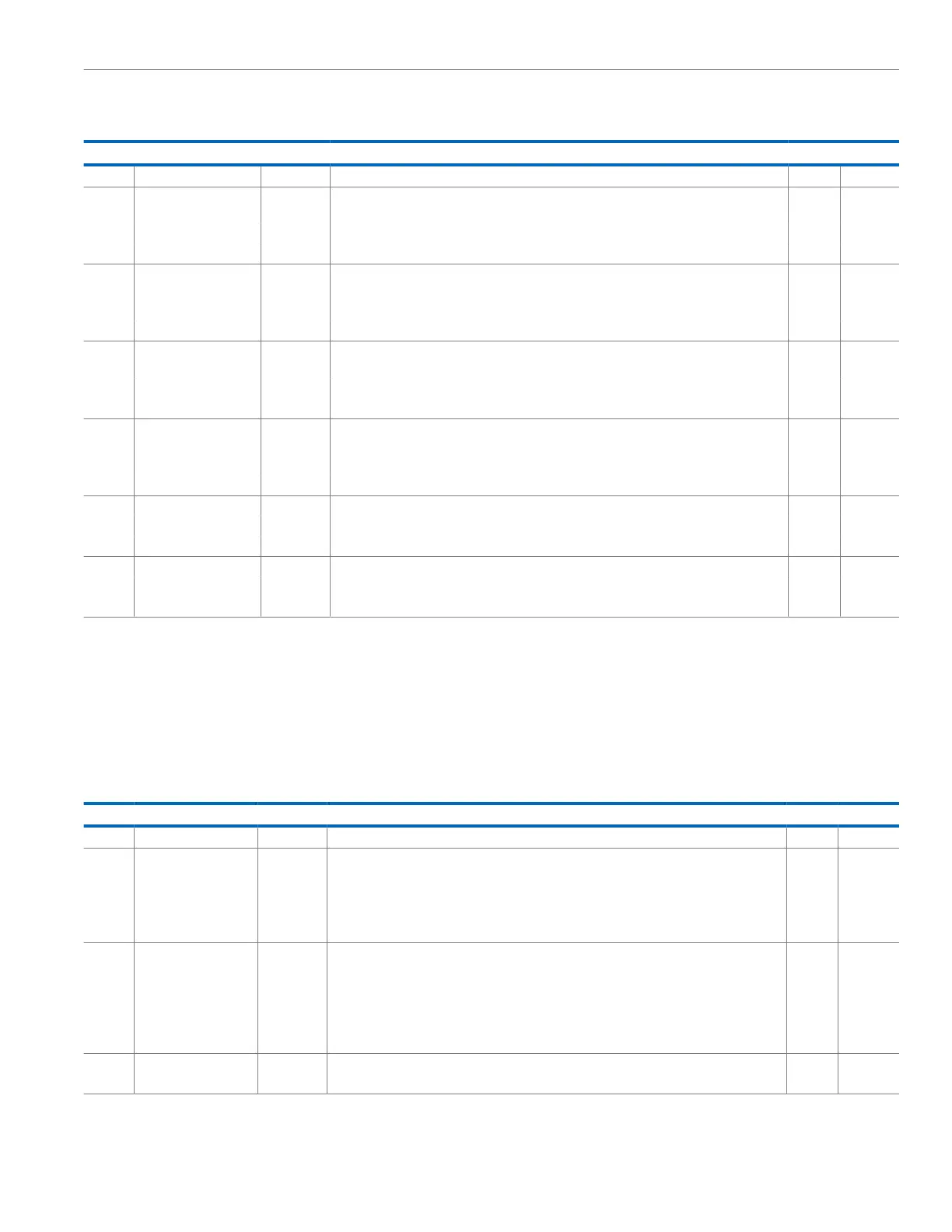

Table 70. Bit Descriptions for ADCINTIEN (Continued)

Bits Bit Name Settings Description Reset Access

1 Interrupt enabled.

5 ADCMAXFAILIEN ADC Maximum Value Check Fail Interrupt Enable. When set, this bit generates an interrupt if the

ADC result is greater than the value in the ADCMAX register.

0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

4 ADCMINFAILIEN ADC Minimum Value Check Fail Interrupt Enable. When set, this bit generates an interrupt if the

ADC result is less than the value in the ADCMIN register.

0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

3 TEMPRDYIEN Temperature Sensor 0 ADC Result Ready Interrupt Enable. The TEMPSENSDAT0 register is

ready for reading.

0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

2 SINC2RDYIEN Low-Pass Filter Result Interrupt. Supply rejection filter result ready for interrupt enable. The

SINC2DAT register is ready for reading.

0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

1 DFTRDYIEN DFT Result Ready Interrupt. The DFTREAL and DFTIMAG registers are ready for reading. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

0 ADCRDYIEN ADC Result Ready Interrupt Enable. The ADCDAT register is ready for reading. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

ANALOG CAPTURE INTERRUPT REGISTER

Address: 0x400C2098, Reset: 0x00000000, Name: ADCINTSTA

The bits in this register are sticky when set. Each bit is cleared by writing a 1 to its location. Writing a 0 has no effect. If simultaneously the

interrupt source is asserted and the core is attempting to clear a bit, the interrupt remains set. A read of 1 means the interrupt source has been

asserted since the last time the bit was cleared. A read of 0 means the interrupt source has not been asserted since the last time the bit was

cleared.

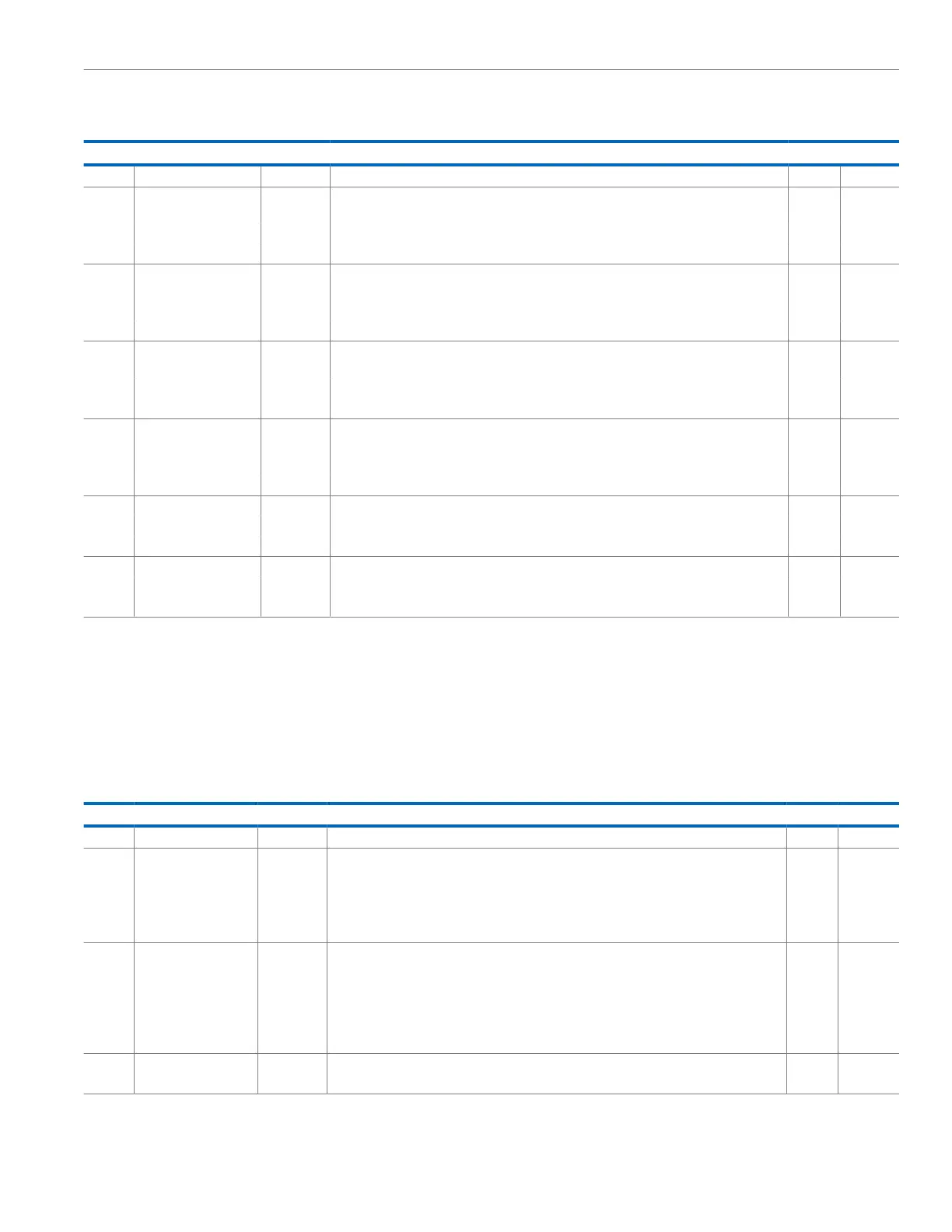

Table 71. Bit Descriptions for ADCINTSTA

Bits Bit Name Settings Description Reset Access

[31:8] Reserved Reserved. 0x0 R

7 MEANRDY Mean Result Ready. If STATSCON, Bit 0 is set to 1, this bit indicates the status of the

STATSMEAN register. The user must write 1 to this bit to clear it. Writing 0 has no effect.

0x0 R/W1C

0 Interrupt not asserted.

1 Interrupt asserted. The STATSMEAN register is ready for reading. This bit generates an interrupt

if ADCINTIEN, Bit 7 = 1.

6 ADCDIFFERR ADC Delta Ready. ADC delta value check fail. User must write 1 to this bit to clear it. Writing 0

has no effect.

0x0 R/W1C

0 Interrupt not asserted.

1 Interrupt asserted. When set, this bit indicates that the difference between two consecutive

ADCDAT results was greater than the value specified by the ADCDELTA register. This bit

generates an interrupt if ADCINTIEN, Bit 6 = 1.

5 ADCMAXERR ADC Maximum Value Check Fail. User must write 1 to this bit to clear it. Writing 0 has no effect. 0x0 R/W1C

0 Interrupt not asserted.

Loading...

Loading...