Reference Manual ADuCM356

REGISTER DETAILS: ADC CIRCUIT

analog.com Rev. A | 68 of 312

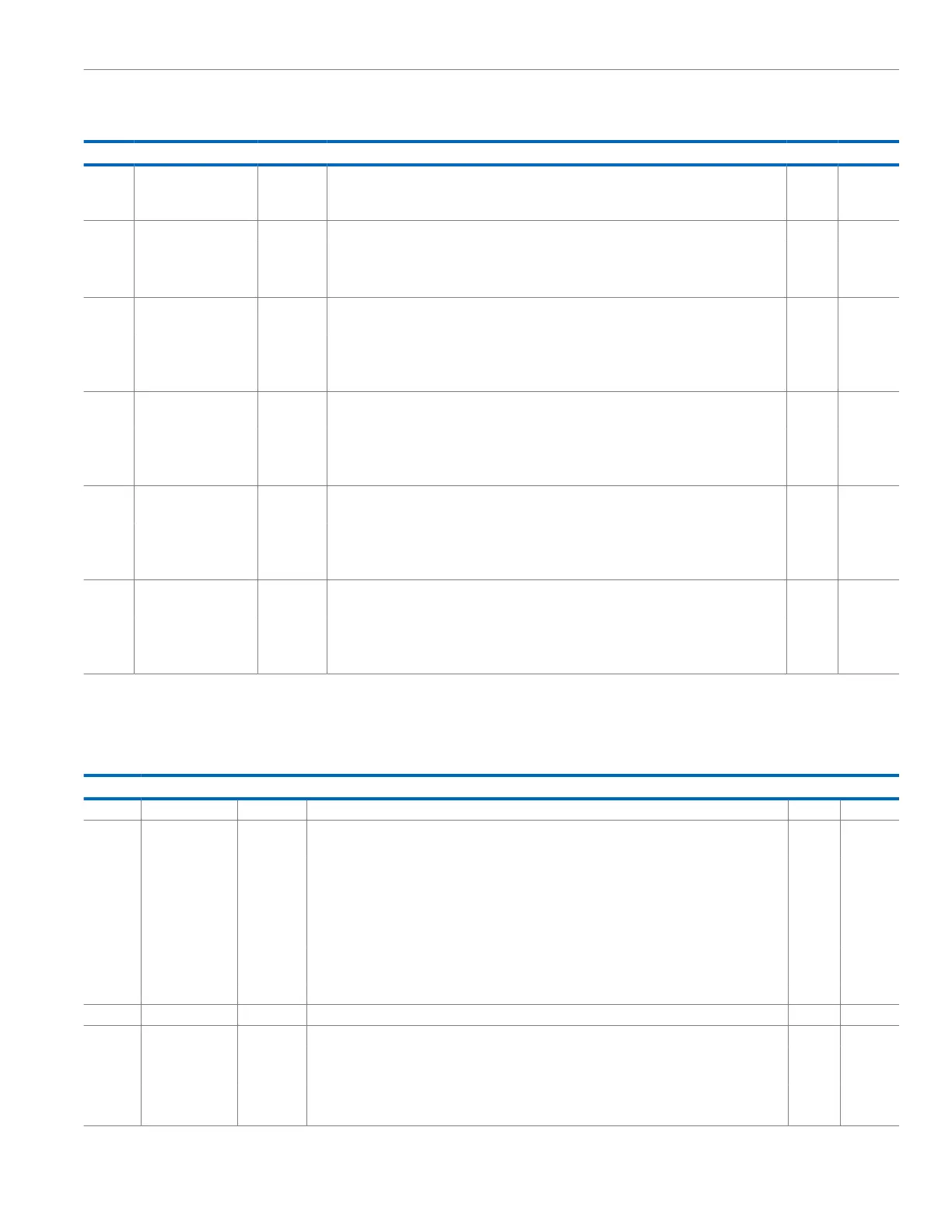

Table 71. Bit Descriptions for ADCINTSTA (Continued)

Bits Bit Name Settings Description Reset Access

1 Interrupt asserted. When set, indicates that ADCDAT result was greater than the value specified

by the ADCMAX register. This bit generates an interrupt if ADCINTIEN, Bit 5 = 1. User must

write 1 to this bit to clear it. Writing 0 has no effect.

4 ADCMINERR ADC Minimum Value Check Fail. Writing 0 has no effect. 0x0 R/W1C

0 Interrupt not asserted.

1 Interrupt asserted. When set, indicates ADCDAT result was less than the value specified by

ADCMIN. This bit generates an interrupt if ADCINTIEN, Bit 4 = 1.

3 TEMPRDY Temperature Sensor Result Ready Interrupt. User must write 1 to this bit to clear it. Writing 0 has

no effect.

0x0 R/W1C

0 Interrupt not asserted.

1 Interrupt asserted. When set, indicates TEMPSENSDAT0 result is ready for reading. This bit

generates an interrupt if ADCINTIEN, Bit 3 = 1.

2 SINC2RDY Low-Pass Filter Result Status. Supply rejection filter result ready interrupt. User must write 1 to

this bit to clear it. Writing 0 has no effect.

0x0 R/W1C

0 Interrupt not asserted.

1 Interrupt asserted. When set, indicates SINC2DAT result is ready for reading. This bit generates

an interrupt if ADCINTIEN, Bit 2 = 1.

1 DFTRDY DFT Result Ready Status. DFT result ready interrupt. User must write 1 to this bit to clear it.

Writing 0 has no effect.

0x0 R/W1C

0 Interrupt not asserted.

1 Interrupt asserted. When set, indicates DFTREAL and DFTIMAG registers are ready for reading.

This bit generates an interrupt if ADCINTIEN, Bit 1 = 1.

0 ADCRDY ADC Result Ready Status. ADC result ready interrupt. User must write 1 to this bit to clear it.

Writing 0 has no effect.

0x0 R/W1C

0 Interrupt not asserted.

1 Interrupt asserted. When set, indicates ADCDAT register is ready for reading. This bit generates

an interrupt if ADCINTIEN, Bit 0 = 1.

AFE DSP CONFIGURATION REGISTER

Address: 0x400C20D0, Reset: 0x00000090, Name: DFTCON

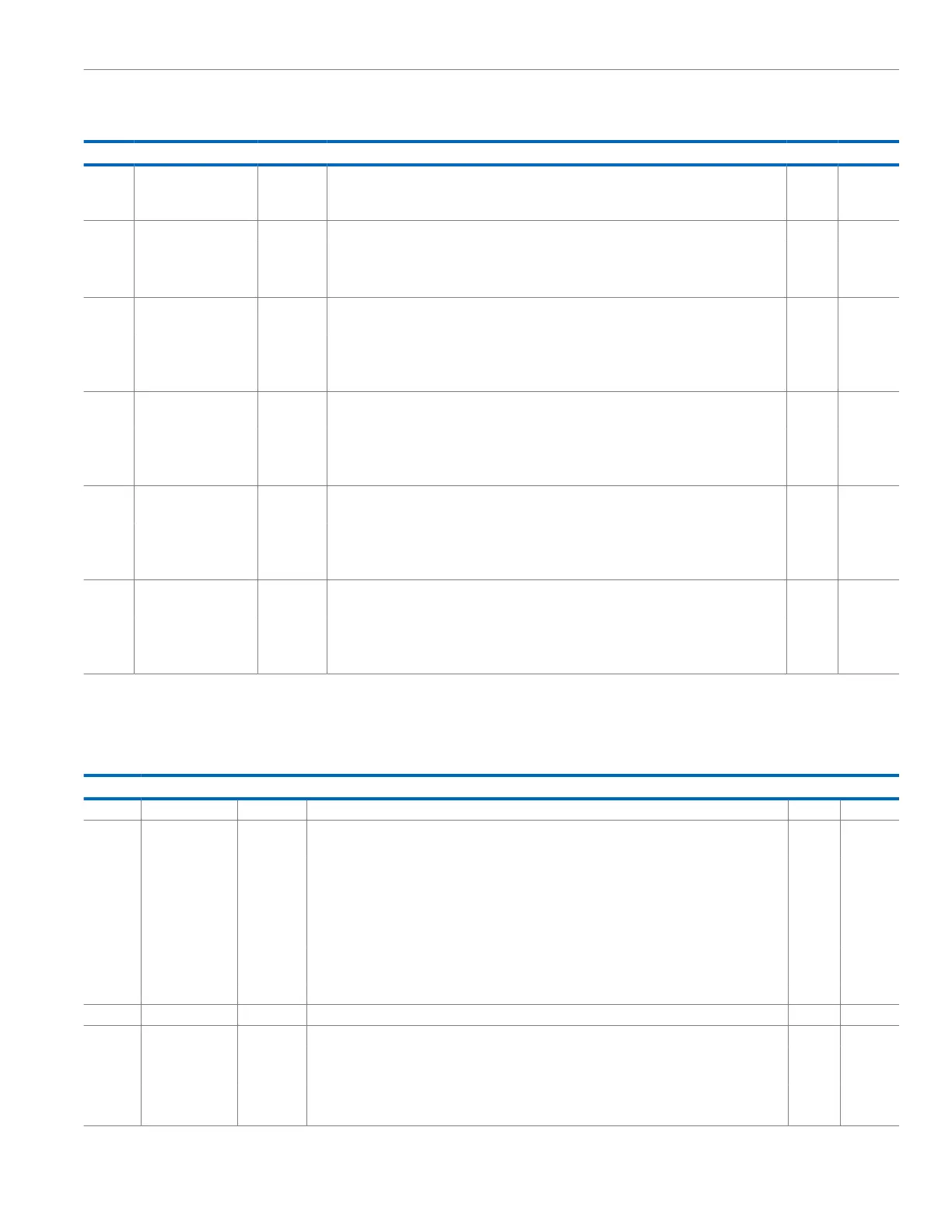

Table 72. Bit Descriptions for DFTCON

Bits Bit Name Settings Description Reset Access

[31:22] Reserved Reserved. 0x0 R

[21:20] DFTINSEL DFT Input Select. ADCFILTERCON, Bit 7 is the highest priority. If ADCFILTERCON, Bit 7 is 1, output

of average block is used as the DFT input, regardless of the DFTINSEL setting.

0x0 R/W

00 Supply filter output. Select output from low-pass supply filter.

01 Gain offset output with or without sinc3. Select output from ADC gain and offset correction stage. If

ADCFILTERCON, Bit 6 is 1 (filter is bypassed), ADC raw data through gain or offset correction is the

DFT input. If the SINC3BYP bit in the ADCFILTERCON register is 0 (filter is not bypassed), the sinc3

output through gain or offset correction is the DFT input.

10 ADC raw data. Select output direct from the ADC, no offset or gain correction. Only supported for 800

kHz sample rate of ADC.

11 Supply filter output. Select output from low-pass supply filter. Same as 00.

[19:8] Reserved Reserved. 0x0 R

[7:4] DFTNUM ADC Samples Used. DFT number is 4 to 16,384. 0x9 R/W

0 DFT point number is 4. DFT uses 4 ADC samples.

1 DFT point number is 8. DFT uses 8 ADC samples.

10 DFT point number is 16. DFT uses 16 ADC samples.

11 DFT point number is 32. DFT uses 32 ADC samples.

Loading...

Loading...