Reference Manual ADuCM356

REGISTER DETAILS: SYSTEM EXCEPTIONS AND PERIPHERAL INTERRUPTS

analog.com Rev. A | 45 of 312

EXTERNAL INTERRUPT CONFIGURATION 0 REGISTER

Address: 0x4004C080, Reset: 0x00200000, Name: XINT_CFG0

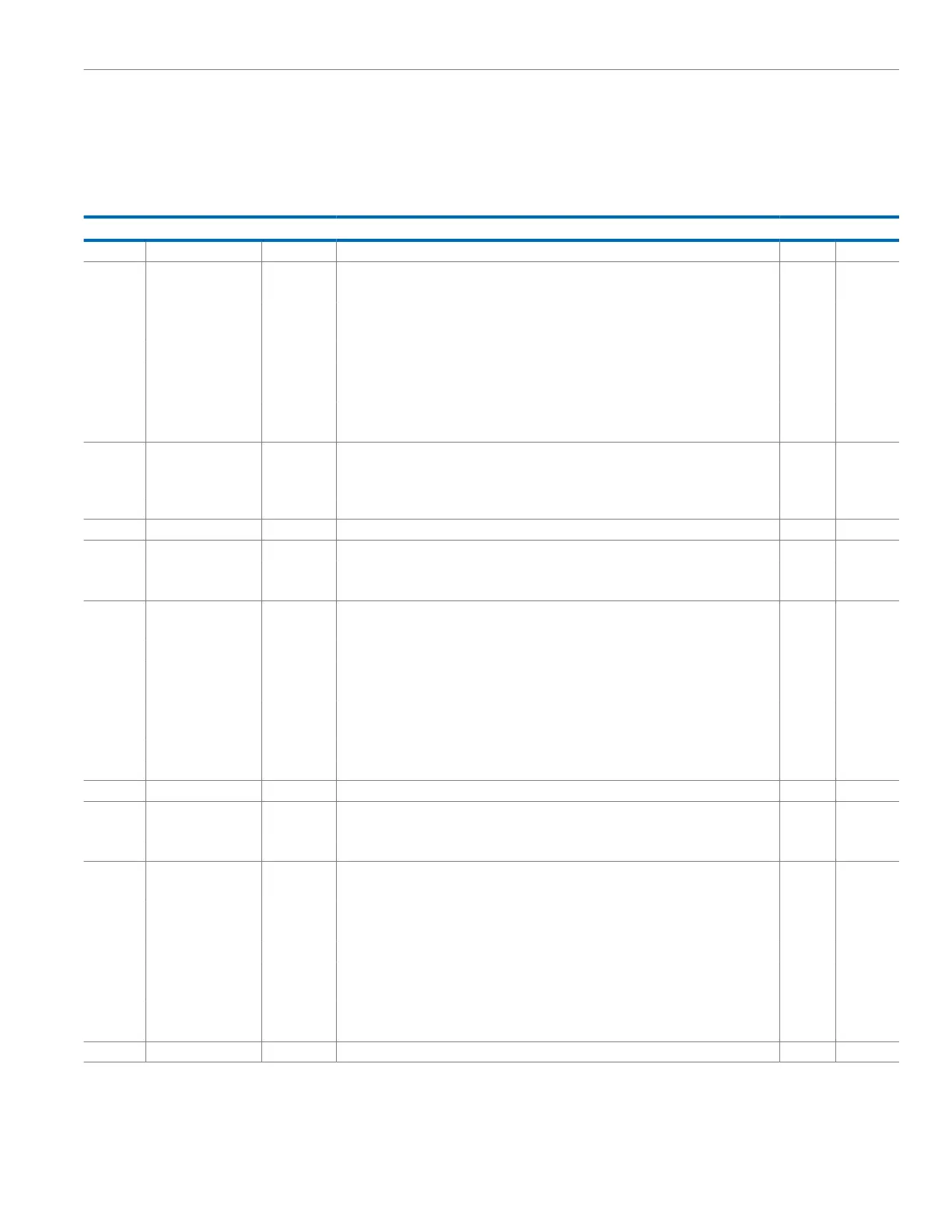

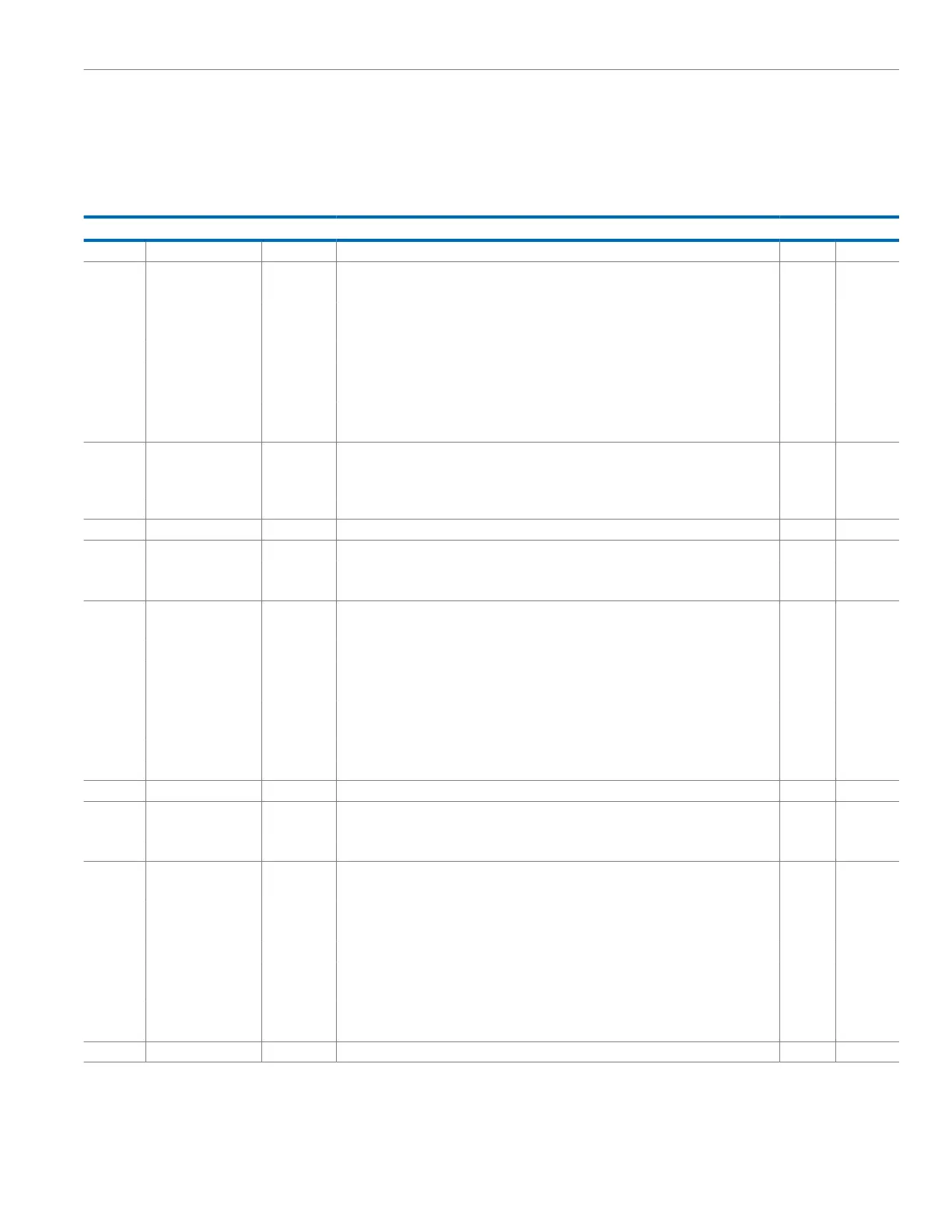

Table 46. Bit Descriptions for XINT_CFG0

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x0 R

[23:21] UART_RX_MDE External Interrupt Using P0.11/UART_SIN Wake-Up Mode. 0x1 R/W

000 Rising edge.

001 Falling edge.

010 Rising or falling edge.

011 High level.

100 Low level.

101 Falling edge (same as 001).

110 Rising or falling edge (same as 010).

111 High level (same as 011).

20 UART_RX_EN External Interrupt Enable Bit. This bit enables the P0.11/UART_SIN pin to generate an

interrupt on IRQ4. Refer to Table 41.

0x0 R/W

1 P0.11/UART_SIN wake-up interrupt is enabled.

0 P0.11/UART_SIN wake-up interrupt is disabled.

[19:16] Reserved Reserved. 0x0 R/W

15 IRQ3EN External Interrupt 3 Enable Bit. 0x0 R/W

0 External Interrupt 3 disabled.

1 External Interrupt 3 enabled.

[14:12] IRQ3MDE External Interrupt 3 Mode. 0x0 R/W

000 Rising edge.

001 Falling edge.

010 Rising or falling edge.

011 High level.

100 Low level.

101 Falling edge (same as 001).

110 Rising or falling edge (same as 010).

111 High level (same as 011).

[11:8] Reserved Reserved. 0x0 R/W

7 IRQ1EN External Interrupt 1 Enable Bit. 0x0 R/W

0 External Interrupt 1 disabled.

1 External Interrupt 1 enabled.

[6:4] IRQ1MDE External Interrupt 1 Mode. 0x0 R/W

000 Rising edge.

001 Falling edge.

010 Rising or falling edge.

011 High level.

100 Low level.

101 Falling edge (same as 001).

110 Rising or falling edge (same as 010).

111 High level (same as 011).

[3:0] Reserved Reserved. 0x0 R/W

Loading...

Loading...