Reference Manual ADuCM356

REGISTER DETAILS: I

2

C

analog.com Rev. A | 227 of 312

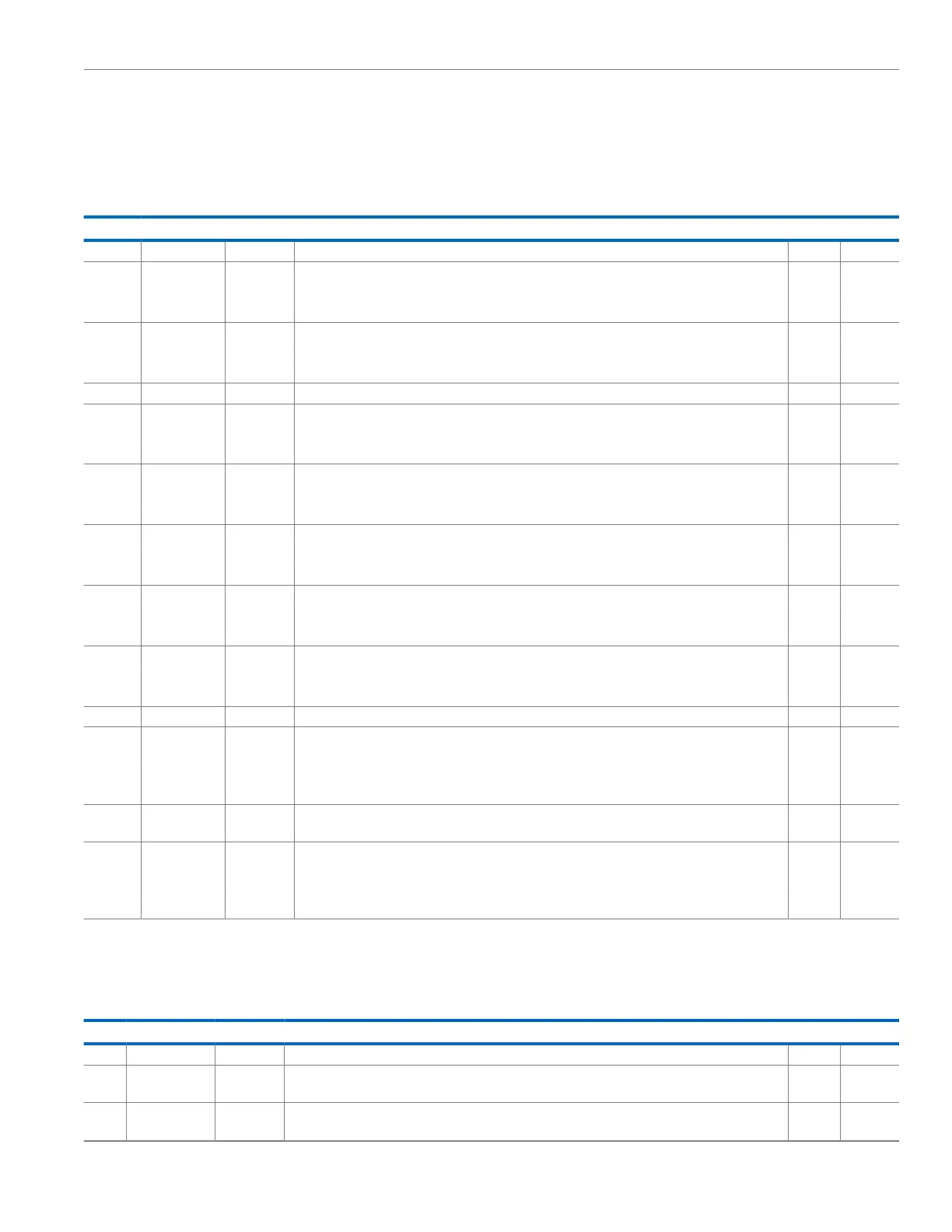

INITIATOR CONTROL REGISTER

Address: 0x40003000, Reset: 0x0000, Name: MCTL

Table 283. Bit Descriptions for MCTL

Bits Bit Name Settings Description Reset Access

[15:12] Reserved Reserved. 0x0 R

11 MTXDMA Enable Initiator Transmit DMA Request. 0x0 W

0 Disable DMA mode.

1 Enable I

2

C initiator DMA transmit requests.

10 MRXDMA Enable Initiator Receive DMA Request. 0x0 W

0 Disable DMA mode.

1 Enable I

2

C initiator DMA receive requests.

9 Reserved Reserved. 0x0 R/W

8 IENCMP Transaction Completed (or Stop Detected) Interrupt Enable. 0x0 R/W

0 Interrupt is not generated when a stop is detected.

1 Interrupt is generated when a stop is detected.

7 IENACK Acknowledge Not Received Interrupt Enable. 0x0 R/W

0 Acknowledge not received interrupt disable.

1 Acknowledge not received interrupt enable.

6 IENALOST Arbitration Lost Interrupt Enable. 0x0 R/W

0 Arbitration lost interrupt disable.

1 Arbitration lost interrupt enable.

5 IENMTX Transmit Request Interrupt Enable. 0x0 R/W

0 Transmit request interrupt disable.

1 Transmit request interrupt enable.

4 IENMRX Receive Request Interrupt Enable. 0x0 R/W

0 Receive request interrupt disable.

1 Receive request interrupt enable.

3 Reserved Reserved. Write 0 to this bit. 0x0 R/W

2 LOOPBACK Internal Loopback Enable. It is also possible for the initiator to loop back a transfer to the target as long

as the device address corresponds, otherwise known as external loopback.

0x0 R/W

0 I2C_SCL and I2C_SDA out of the device are not muxed onto their corresponding inputs.

1 I2C_SCL and I2C_SDA out of the device are muxed onto their corresponding inputs.

1 COMPETE Start Back Off Disable. Setting this bit enables the device to compete for ownership even if another

device is currently driving a start condition.

0x0 R/W

0 MASEN Initiator Enable. The initiator must be disabled to gate the clock to the initiator when not in use and save

power. Do not clear until a transaction has completed (see MSTAT, Bit 8).

0x0 R/W

0 Initiator is disabled.

1 Initiator is enabled.

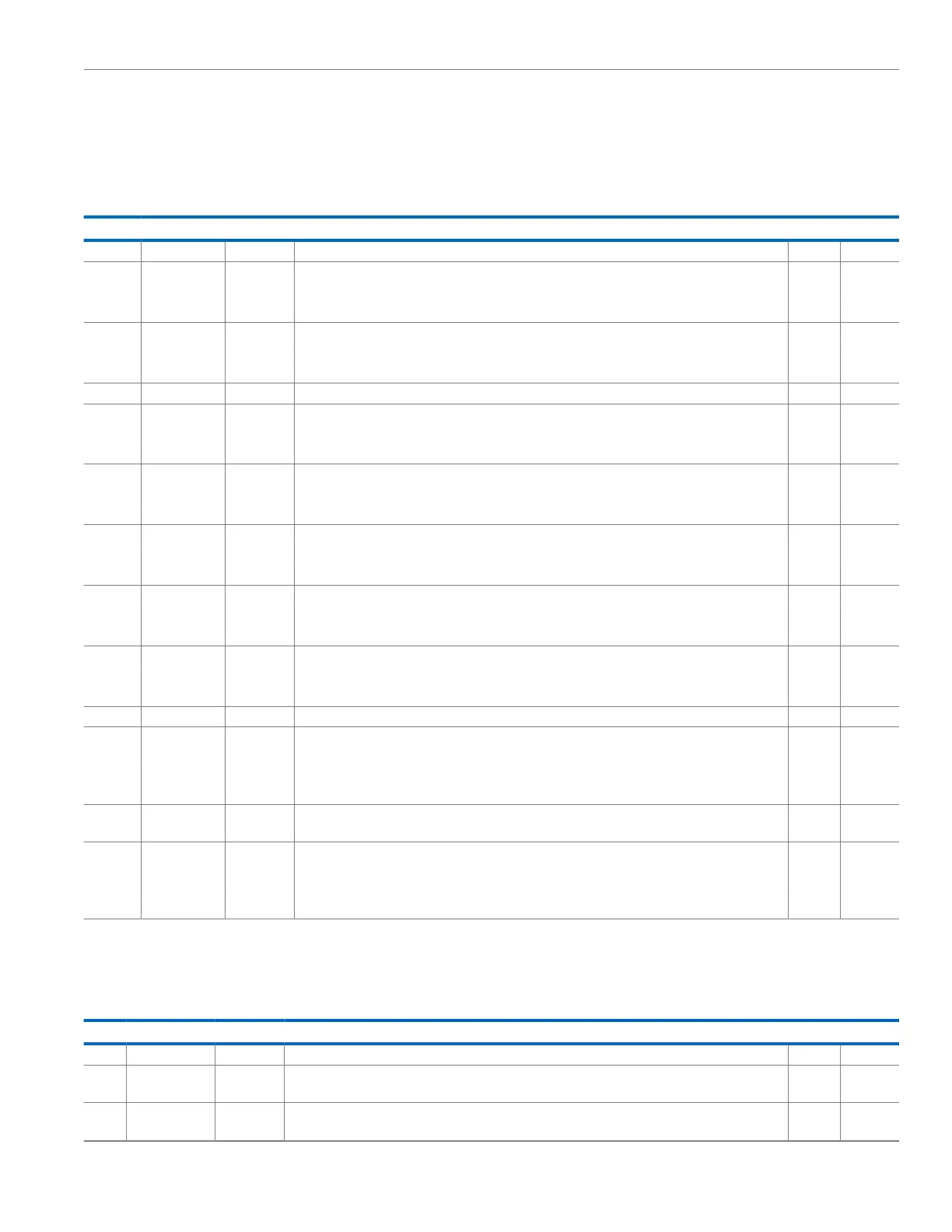

INITIATOR STATUS REGISTER

Address: 0x40003004, Reset: 0x6000, Name: MSTAT

Table 284. Bit Descriptions for MSTAT

Bits Bit Name Settings Description Reset Access

15 Reserved Reserved. 0x0 R

14 SCLFILT State of I2C_SCL Line. This bit is the output of the glitch filter on I2C_SCL. I2C_SCL is always pulled high

when undriven.

0x1 R

13 SDAFILT State of I2C_SDA Line. This bit is the output of the glitch filter on I2C_SDA. I2C_SDA is always pulled

high when undriven.

0x1 R

Loading...

Loading...